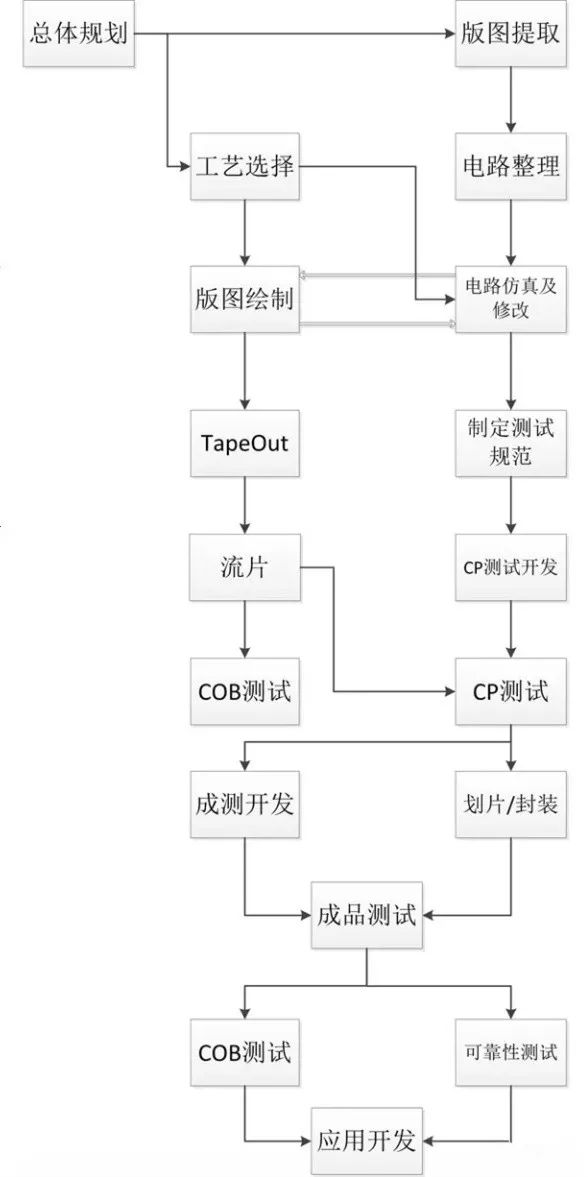

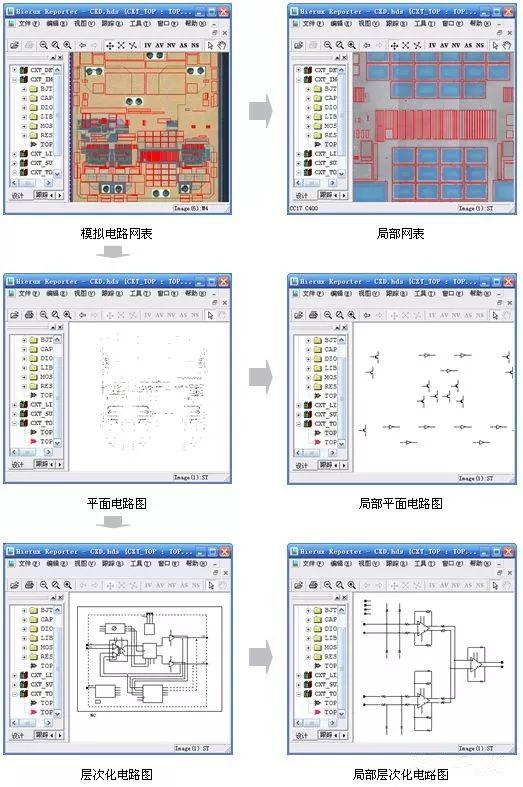

什么是芯片反向设计?反向设计其实就是芯片反向设计。它是通过对芯片内部电路的提取与分析、整理,实现对芯片技术原理、设计思路、工艺制造、结构机制等方面的深入洞悉,可用来验证设计框架或者分析信息流在技术上的问题,也可以助力新的芯片设计或者产品设计方案。5 i8 P$ p8 ?. d& t6 s3 \. f

什么是芯片反向设计?反向设计其实就是芯片反向设计。它是通过对芯片内部电路的提取与分析、整理,实现对芯片技术原理、设计思路、工艺制造、结构机制等方面的深入洞悉,可用来验证设计框架或者分析信息流在技术上的问题,也可以助力新的芯片设计或者产品设计方案。5 i8 P$ p8 ?. d& t6 s3 \. f

UT板有时候也叫针卡);4,自制测试仪(可选),当测试仪并不能完成某些特殊测试项的要求时,还得自己制作测试仪。例如,红外接收芯片测试所需要用到的扫频仪,若采用非自制扫频仪,测试时间将非常长,必须自己制作。5,测试数据的分析。对测试数据的分析有助于对测试方法的改进和对芯片设计的改进。CP测试在整个芯片反向设计中占据着重要位置,所花费的人力、物力是非常多的,还需要频繁和测试厂交流,所以CP测试显得非常复杂。在CP测试开发完之后,会进行COB测试,之后才进行CP测试的调试阶段,以及正式批量测试阶段。0 y: J% i1 @4 a, w

UT板有时候也叫针卡);4,自制测试仪(可选),当测试仪并不能完成某些特殊测试项的要求时,还得自己制作测试仪。例如,红外接收芯片测试所需要用到的扫频仪,若采用非自制扫频仪,测试时间将非常长,必须自己制作。5,测试数据的分析。对测试数据的分析有助于对测试方法的改进和对芯片设计的改进。CP测试在整个芯片反向设计中占据着重要位置,所花费的人力、物力是非常多的,还需要频繁和测试厂交流,所以CP测试显得非常复杂。在CP测试开发完之后,会进行COB测试,之后才进行CP测试的调试阶段,以及正式批量测试阶段。0 y: J% i1 @4 a, w| 欢迎光临 EDA365电子工程师网 (https://bbs.elecnest.cn/) | Powered by Discuz! X3.2 |