6 ^, o1 ?9 u% o/ u9 M: vTapped routing 优势在哪里?

! V% r) r' T8 z0 H8 R本期作者:愈延峰 ,秦真水,邵鹏,Amanda,李劲松,谭树杰,龚艳鸿,曹小华,Roder ,郑琪,欧阳,张吉权 ,郭永生,敌敌畏,毛毛虫...等 $ @0 K( d/ C7 i7 g! C- M

他们来自:ZTE,浪潮特种计算机,IBM,Cisco,Nubia,承泰科技,汉普电子,浪潮服务器,Ansys,大唐微电子,烽火通信,迈普通信....等企业 |

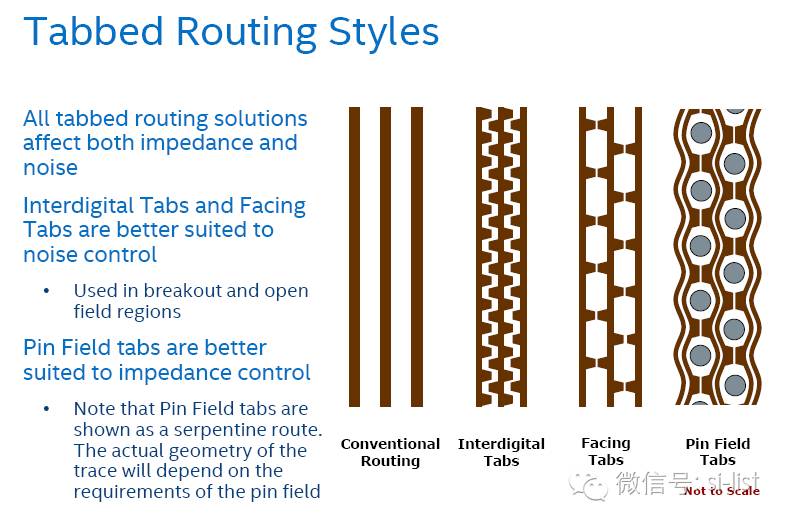

名词解释:Tapped routing由intel公司2015年3月份提出,主要用在下一代处理器SKYLAKE平台,DDR4的走线方式。走线如下图方式:  " Z3 G1 ~( g' i& y; l& ~7 z " Z3 G1 ~( g' i& y; l& ~7 z

|

微信群"SI-list 中国【1】"聊天记录如下:

7 b Z' a( g ^0 \' c( J5 ?: V! s

————— 2016-5-23 —————

yu 上午10:02

2 T5 k6 K2 b, Y9 q% B4 l+ Y, G # Q' q8 X/ j0 r: j

) u0 X. c2 p8 R

# Q' q8 X/ j0 r: j

) u0 X. c2 p8 R yu 上午10:05

& S3 E% P& q( K' z( z6 [) xIntel tabbed traces效果分析[微笑]just so so, 打算下月申请做个测试板。群主是不是免费哈[微笑]。所有测试结果全公开; j* }$ K( J/ \! r' n' d: v

. H2 E* E% `1 f i! _9 ]' C7 `

李黎明 上午10:07! r7 q+ N" |$ k. P; l$ H

可以考虑比较下。。。[呲牙]) l9 a* E$ T4 F& ]4 _& |& @/ |0 M

# v4 Z- ?9 o" D( R7 E- N

晓月独赏梅 上午10:07' `7 G, K4 s* }' \

@yu [强]# b3 B8 T: ?' `* y0 i6 b

2 ^6 g2 E* I0 n, V2 ?

晓月独赏梅 上午10:078 N8 r. m' o- w- f8 Q$ K1 r; J! n

这个可以有

+ z- [+ Y: T/ s4 g7 n" {3 Q; C# {; O* |9 [; b

邵鹏 上午10:08

$ r3 K0 I0 F5 E" p( l/ |4 D@yu 那个TabRouting就是Intel拿出来吓唬人的东西。没啥好处,还增大串扰。很早以前我只是定性判断过。你能给数据最好 Q G# x$ r

不是减少串扰的把,是减小线宽突变带来的振铃

5 L+ i0 |/ X4 Y' h# U$ }

, ?0 o: p: M$ F1 d _1 F* E

Colin 上午10:12

- R4 V2 j6 B- Q1 i& X5 D. O串扰会不会增大不知道,没研究过" Z3 z' p5 m2 T

" l7 u: `3 V2 [+ q' X, Q) {

yu 上午10:13' ] N) G0 @0 }6 B& ~

@邵鹏 [微笑] intel的东西不拿出坚实的数据,大家不敢不服从,除了我[微笑]& U2 ]; n% I4 z1 M) i% }- t! t

8 f( Q. H8 T- D% ]: ^: {2 p w

Colin 上午10:14

: _& ^( {- ]% A2 b/ s@yu 期待测试数据

5 O5 e: Y" M. w. J' U- j- U+ _9 [& V

eletan 上午10:14

$ j, v4 Z( ]$ n/ D+ ~1 w" {0 P % x {( P9 C& E7 a& i# \7 B; \0 c/ F' c( M0 @

% x {( P9 C& E7 a& i# \7 B; \0 c/ F' c( M0 @

Amanda 上午10:15

' Z; X5 u( n1 a% s" r) m 0 ?8 V6 U* k+ r$ y. A7 l$ @/ D8 l5 Q" n6 y

0 ?8 V6 U* k+ r$ y. A7 l$ @/ D8 l5 Q" n6 y

eletan 上午10:15

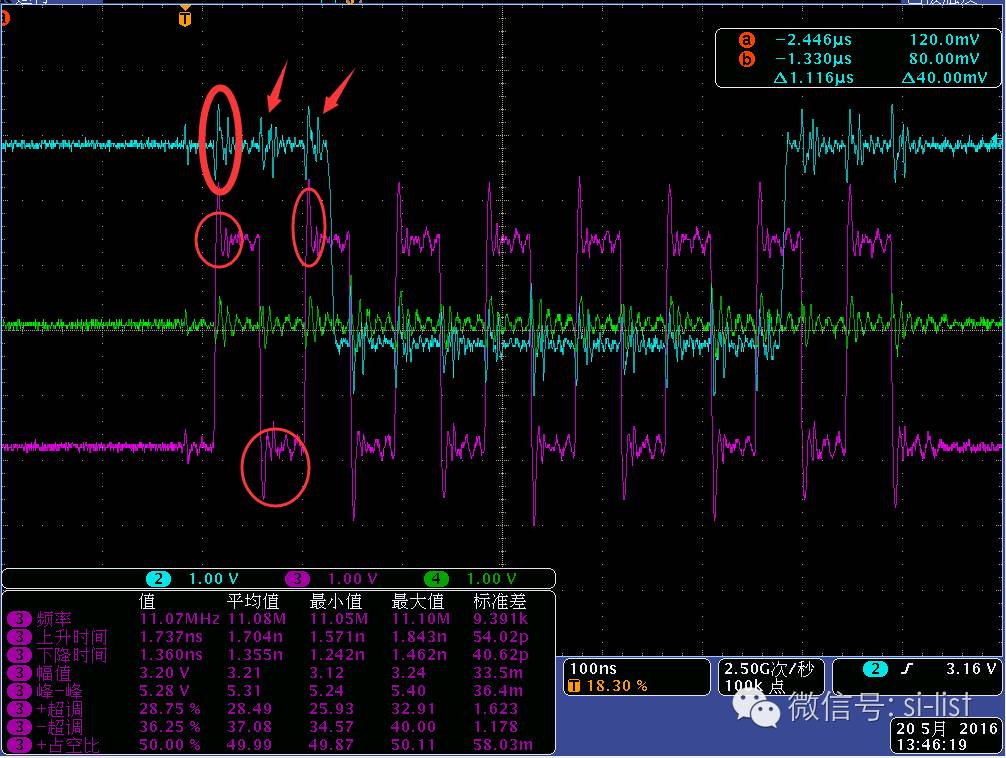

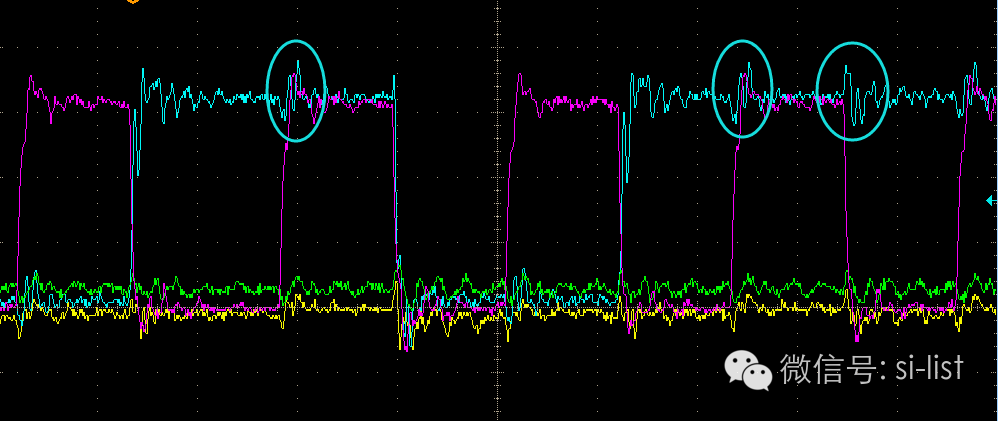

. s0 ]# p" V# }0 k; I& N这是SPI总线的实测波形,是什么原因导致以及通常有什么措施去抑制呢# ~" {( c. m2 P

- o; e R' Y$ J. [, h

eletan 上午10:16

! C$ O8 O0 }1 L3 S2 p+ n3 W蓝色线即使在高电平或者低电平,也随着紫色时钟信号也规律性的出现波动

, F& t# {6 O4 R

1 J% r! P& \ F* G

eletan 上午10:17

! M8 N) J% h" u! v绿色的使能线,低电平出现同样的纹波

* G% K( n, I3 J" e+ {" m/ p6 h0 b/ r! h; f

Colin 上午10:17! Z" R/ L5 ^; ^& o/ L6 j

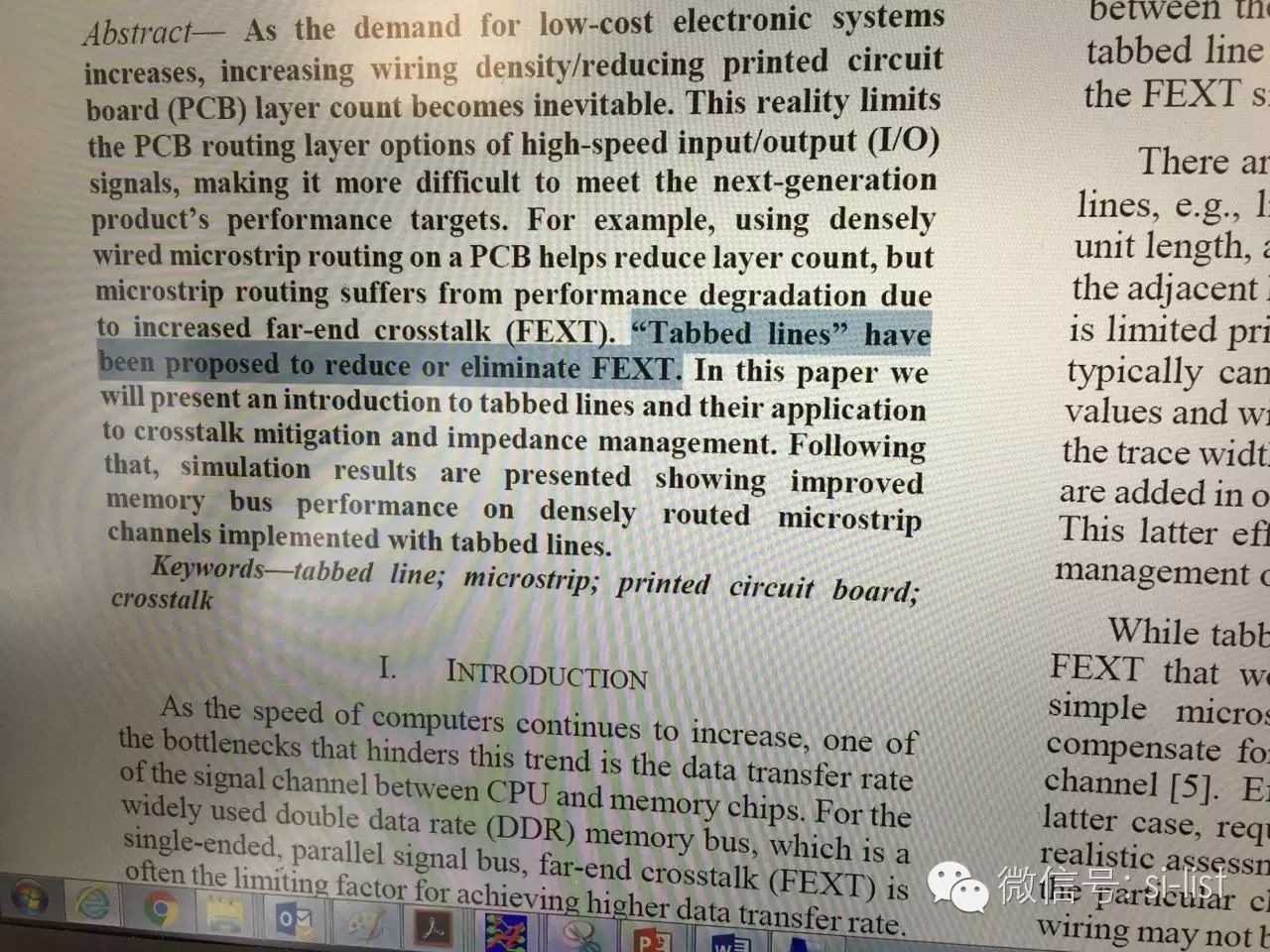

@Amanda 怎么减少fext?原理?/ E1 f# `: Y4 \

9 H: H/ q3 g5 V" P" B+ E

yu 上午10:17' q; C. e+ ]1 h: B1 p# e

@eletan 示波器接地要保证好,另外也可注意别用过于宽带的示波器;如果这些注意后还是如此,和芯片上升沿太徒有关。谁让工艺提升太快呢[微笑]

+ M, ~- M; ~+ y" J& ^9 a

6 j4 E! U% e+ t1 k' F

邵鹏 上午10:19

# a; u) G) H: D: u( z% n@eletan 你这应该是明显的阻抗不匹配引起的振铃$ q" R; G8 W' M; b: u

' R2 a$ n) g9 V* g1 k. _

eletan 上午10:19

e8 k( J7 c6 S/ b@yu 蓝色MOSI和跟随紫色CLK同步出现纹波,这种是什么原因?电源滤波?

8 h/ D/ f1 S# x( c0 e* W" k

6 u4 ]1 e( N: F

eletan 上午10:20

7 p+ T( l. N5 H$ W- K串的电阻由0欧换成33欧,明显变好,但是这种同步出现的纹波依旧存在

0 F: l9 i" K0 E6 ]2 y& z

/ V- S. R# o: @# j7 C3 |+ s; r" H

eletan 上午10:21

6 X( s& k; a, r5 ?9 t x k- G/ F" v% u6 s7 }" O9 ^6 K, H# u

k- G/ F" v% u6 s7 }" O9 ^6 K, H# u

邵鹏 上午10:22

( L+ K& k& Q; Y2 |@Amanda Intel的论文有时为了强调某种效果,在分析数据时故意忽略掉一些不利因素,以突出它的结论。但现实使用中往往不像它宣称的那样。# p; O0 F; O2 L, o# ]; F/ l

& R/ ]. |7 r. N5 h8 r4 ?" D0 r

yu 上午10:23

" u4 o& b) b# K5 X/ m/ N, W不光是Intel,太多的人为论文和专利那样做[微笑]5 a. @8 z+ V, x

. \/ u E) P# m; q

yu 上午10:247 c- C3 c% C( h) I% ^

@eletan 用低带宽探头测一下地弹

; @) P5 D2 V& A4 ~; K# u8 \7 y0 l1 ~9 G% N; ?" c

邵鹏 上午10:24( ?- c* R/ r& y8 R* X Z

@eletan 抱歉,蓝色波形和紫色波形我没看出相关性。蓝色波形有它自己的问题。1 d8 g9 Z# c& T$ K

/ c0 k. o6 q3 N' W# ]8 n

eletan 上午10:246 M) b' \; d+ u7 P$ V, Y

是不是他俩走线靠太近了,最近的距离0.3mm,大多在0.4~0.5mm间距 w( m4 e0 c ?$ g s, u5 x T6 k3 U

7 [ x) x' i& u' P

邵鹏 上午10:24! {+ b2 H; t! G0 l5 D% C+ ?9 I0 [ R

电源肯定有纹波

, j( h# y; Q& z

7 w4 E2 H, W' e5 x* [- l; |% F

eletan 上午10:255 L" o, ]. d; j% D! G/ r

1 I9 K, A# u7 e2 H$ K7 F

9 z$ e' D1 e B0 k/ j$ d

1 I9 K, A# u7 e2 H$ K7 F

9 z$ e' D1 e B0 k/ j$ d

eletan 上午10:257 ?3 \: l/ j& h4 f

就蓝色的高电平也会出现纹波,恰好出现在CLK的跳变沿

8 \& A' Y: V! m8 G0 P/ b" K6 f: U# y: q5 \( v; e( |

eletan 上午10:26

0 U6 I, k9 M- l" _CLK一上升,蓝色就被拉下一点然后反弹,下降则相反

; x7 B8 e$ x3 {! j6 _6 i4 i) p- p/ k! [: P P/ N( D

邵鹏 上午10:265 U1 s" v8 \$ u5 n! S

@eletan 看到了,蓝色不翻转的时候,随红色沿跳动 E" X- ?1 {0 X7 B% G) c1 h( ]# D

& Q6 b- S) \7 \/ d3 e

eletan 上午10:26; p+ c; ?+ J; D& n3 g3 g

对0 v+ o0 A8 x3 A8 O+ P

8 n2 |7 T Y5 l7 q, I

邵鹏 上午10:26

0 N/ H0 _" k+ w4 t这应该是FEXT

+ t/ ^0 y3 C. w W* B9 g. M2 i6 a5 s( K$ T& y* P

eletan 上午10:27) F! S% b6 Z) p/ |7 y) I

就这个情况,真的是电源不好?

' U. M% Y5 t' b6 H) X& b

( ]/ b; [5 Q6 T0 a

邵鹏 上午10:28

0 p8 ? I& p8 I L8 m6 k你所有的波形在1,0电平期间抖动,这是电源噪声特性

6 k4 ~2 k7 S: f# `8 \; j

( Y- b) e7 u% f9 R1 s

邵鹏 上午10:296 M' C' V% |) `/ O, w

蓝色随紫色沿跳动,而且极性相反,这是FEXT

( Z- S* X4 ?4 y7 {4 j7 r+ f0 G1 B' ^) K& `+ u, k ]

eletan 上午10:30

9 q% I1 B/ C# \ t0 J# |实则电源纹波在19mV以内 X3 A' d& f- v/ [7 ?

: I/ W/ k% f* n/ H) N

eletan 上午10:33

6 z2 i' J5 J/ w4 G9 z/ p9 e- ]+ M@邵鹏 @yu 非常二位感谢指导4 q- b9 B2 a2 A" S c& G

! D$ ]" b7 O9 t8 z. r$ v$ z+ z: {9 D8 S

Colin 上午10:34

" ~% ^' H6 G9 n/ {: s可不可以视作ssn来解决?这与纹波关系其实不成直接关系[微笑]

9 z3 Q2 d9 T& ]

. E) }/ e) G! @

Amanda 上午10:37. t% {+ n6 I7 a j- V8 m3 L, e5 E- e

@Colin intel的观点是采用tabbed routing,互容会增大,但是互感仍然保持不变,所以可以改善fext

. ^; [! D" B: w2 X5 B) ]6 w; J6 E. {) v0 {

邵鹏 上午10:38

4 T+ r* }2 V+ L' S@eletan 看绿色信号的噪声似乎不止19mv, J y, l) q! }' Q% ` l$ C0 b) |

( P ^( ?" R+ t3 _8 [% D3 b6 o

eletan 上午10:38

9 s% r3 t" T' J- X2 j i# Q3V3电源, I1 f0 B( H3 f# P( B6 W

0 k3 ^6 C7 n/ A' c$ G* W! V

Colin 上午10:39

: i$ \/ Y- u1 M/ X@Amanda 可是,互感也是随着耦合长度增加的呀) l4 a+ t( k: U/ ~5 N* n

4 L* e ]# g! [) l+ a

毛毛虫 上午10:39

1 E4 G" \$ i0 d6 Z" m0 s1 _@eletan 你不要同时测SPI_CK和SPI_MOSI信号,你只用一个探头测SPI_MOSI信号,这时候看看在高或低电平的时候还有没有这种和clk同频的noise,有的话就是FEXT,没有的话就证明是示波器接地引脚引入的noise; N v f* o9 z* z

, l+ y2 e$ y! X. F5 v/ F9 r

Colin 上午10:407 r, c0 P- D7 V- Y

而且互容增加forward应该更大吧$ g) e5 s# A/ ?% G1 }2 X( }: R

) ]) O& Z: d8 @0 M

Colin 上午10:403 }7 d, Z) }/ D" C6 z

[呲牙]3 e U3 W: g1 X: [7 Q. L% l3 q5 G( K

4 f/ C f. |, @8 o, f

邵鹏 上午10:402 |& O8 r+ f) Y' d2 u$ q

@Amanda 他们忽略了,当最TabRouting时,自感不变,但互感增加

# L; x5 H8 j/ b$ P, T3 g. k' z7 q1 n

Colin 上午10:41

9 V0 ]4 t# ^1 ]7 h, u# `所以我认为tabline应该主要目的不是改善串扰

5 v6 Q( h4 z) s: K

. w4 U0 x; d% U5 E9 T2 ^

Colin 上午10:41. l0 G& m8 B2 z% p% [0 y$ y4 V0 l

补偿突变走线的阻抗变化还是有可能的

. _4 ^" C# A9 u1 D: c l; S( N; V3 u4 N) n. d8 e1 t

Amanda 上午10:42

( Y0 ~, X/ s3 l; [3 g我更正一下,intel说的是互容显著增大,但是互感增大不明显

/ k+ `8 ?' w+ ~5 z' n: \8 @% V- O3 v2 p

Colin 上午10:43* ^! L- _" g/ b+ W8 Q- a' L

那这种线是用于微带吧,实际确实在一定频率范围内互感互容体现的感抗增加速度是互换的0 i; j; R# \6 K' ^

! R% k" R' P/ x9 z5 r& l

Amanda 上午10:441 _1 }! U7 O3 ~# @6 k2 |! _

fext由两部分组成,容性和感性,对于不均匀结构,一般是感性大于容性,所以增大容性应该能一定程度上改善fext。但是改善多少,这个tab routing效果到底有没有,有多大,这个就没验证过了

' e' k# k5 [& T! A

5 O- G6 ~0 j/ ]3 o

Colin 上午10:44

8 h L: ?4 T" A) E' n一定范围容大,一定范围感大

$ M! M9 W: P* b

% G, ?* v1 a, Z. y! u& F6 S5 }

邵鹏 上午10:45+ E6 j4 e4 o' e

@Colin 对,TB的初衷是在保证信号安全下,改善阻抗,增大布线密度, Q' f4 |6 l! D+ d- t

8 d$ _8 w, T6 i/ V h1 u7 g4 W3 ~ @

Amanda 上午10:45

( q' ]- F6 e5 [/ T我觉得应该是用在微带上3 P8 |. l/ Z( k7 j; ?9 S

/ y% ^% k0 p# l/ d# K% N1 E

Colin 上午10:451 O2 p. b. S4 A4 p% u5 \- x p

而且互容大,会对fext变差做贡献才对呀" I$ Y6 S6 p* P; j) b8 _) A' @

9 M1 m" f2 q0 y" _+ l* J H" N

Colin 上午10:47

8 `' f0 y: g' H一般改善fext都是减小互容补偿互感,特别是奇模情况下

6 q4 h$ g6 P! N# \* X

1 y( n( ?1 \3 X N4 n) A: l3 \+ C

Colin 上午10:48& x/ ?. {' P, z) P" U8 Y

@邵鹏 我认为这种线对振铃还是有效果的,串扰不好说,用在带状上应该不错[偷笑]

( ~2 I( l7 D ~, i) M, t3 S

. z& R& V3 t% _

yu 上午10:55. k h$ ]; ?3 C0 n- X, D

Intel tabbed trace用于控制表层芯片出线密集过渡段因线宽细同而引起的阻抗上升和降低线间耦合,有些效果,只是just so so[微笑][微笑][微笑]5 p1 L- n; s- k' ~% F. C( E9 K. J

& `" ~: _$ z5 Q; C/ L" B1 ~+ i4 T

Gavin 下午12:11; `2 l6 r+ V4 B- d

任何规则都是有前提条件的,弄清楚其应用的背景才能有作用,不然是看不到效果的

[0 H% z! y2 D6 P

GDDR5仿真优化

7 w* {6 i+ M/ l+ N: v. L敌敌畏 下午4:11# o3 N0 ~0 l; c8 k$ m5 `

请教大家。hspice中,眼图用的时钟激励源带抖动的用哪个源,pu?,带不了抖动?( {/ @: a% K& n" E! [. z6 H

- B i: V% F- X* e* n" V5 b9 f* {$ I

Andy Cao 下午5:48

' X" ]: u2 M% S7 m请教大家一下,ddr的die和rank有什么区别 J5 Q) v2 ?. a. T2 F j9 I0 f# e

2 z6 Z" ]. _' C- O" c9 t4 W

Rodger 下午5:52! j3 Z# }% j6 n8 a0 j

一般凑够64个io就是一个rank

2 L8 @$ D5 t0 X6 w( L+ ?7 I1 I- I4 J0 D0 F

Rodger 下午5:55) M) q* V K# _" G' A# Y2 [0 B

64个DQ,说错了: ^6 p6 l' A6 k. V; n

# |( k7 ~% h( m3 T

Andy Cao 下午5:55

. ?- l6 B0 x N# w* _8 e那怎么理解一颗芯片有多个die

# A. Z9 D+ {$ A

7 b' s" D9 E4 J" h) T L& T: \$ s

yu 下午6:00) f+ V" ~. Z" g$ w9 b: d$ M

Rodger和您解释清楚了3 `/ p& X4 {% x# t. H

- N, h* s: O% ^0 j9 D2 r/ K

yu 下午6:03$ a& I( r2 V$ [2 m$ e

颗粒厂家很少作64位宽的die,因此应用上需多粒拼接。如果是8位的,则要8粒拼成64位。

1 u" J0 [" P t# f! _9 a: |4 k2 l

/ F+ J8 q( }0 i$ m) W, A3 N8 l

yu 下午6:05

~. m; {- O0 u: A7 oGddr5位宽128位。

; ]! P8 Y1 \; S& n1 ^ y: Z

/ _0 g {7 t; Z$ H! b& s

yu 下午6:06

' v; K8 {1 k& u' L. X' K颗粒厂家通常只做4,8,16的4 t6 Z8 q$ G/ I9 K! _5 o" i

% s8 d" T# @' l1 W' D- h* `

yu 下午6:088 I2 n' }8 u/ z. s! R! X

现在还有512位宽的。如何办?这就是rank的工作[微笑]/ l9 O' |3 c& G

* P' N' {$ X1 j9 j

Andy Cao 下午6:08" V' ]5 w# f/ ^% L7 H, S

谢谢@yu 大师,128位是不是得8颗16位gddr5组成,而单颗gddr5颗粒里面有2个die,可以这样理解吗,大师) s& ^ |/ E7 ~; ], A

3 k) _& w" y) N) O+ l

Andy Cao 下午6:10

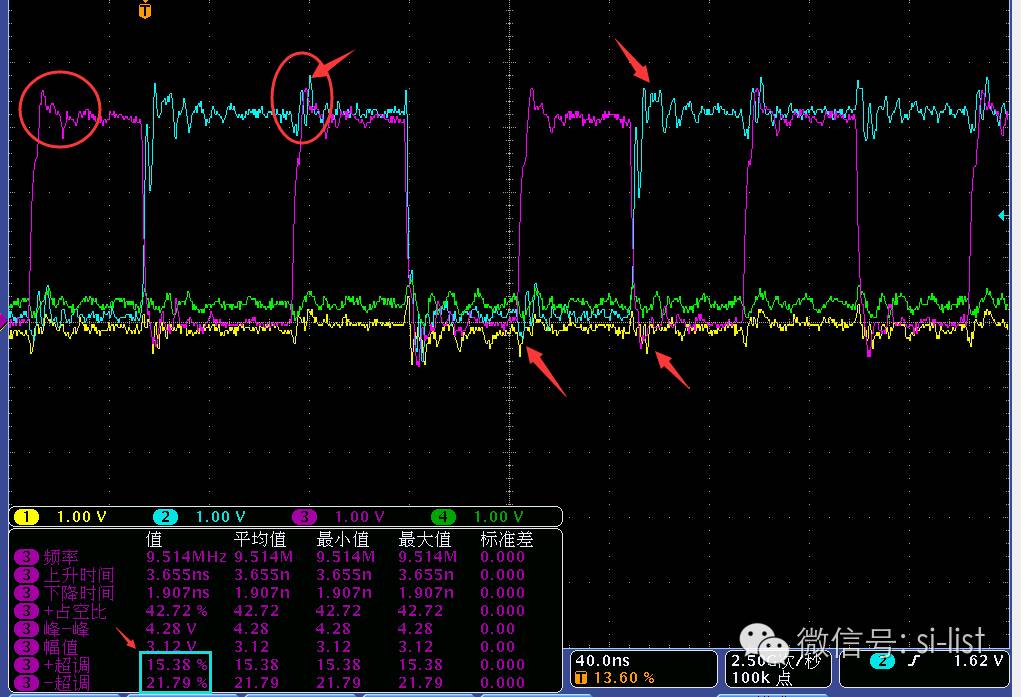

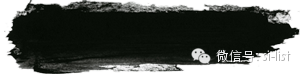

6 ]) }/ f P( w. I( [现在我们测试GDDR5,ck波形非单调,而WCK的波形是好的, X8 E. K- ^3 u/ W

4 Y. b# f# I% S' d0 h

Andy Cao 下午6:11

" F9 C+ J5 ~! n m; J4 f这是啥原因

0 x2 Z/ e( L; C. x# G$ H4 O8 \2 p0 G' d

yu 下午6:12

# c. A2 L0 V+ A; q+ Y: JRank不等于Band

! x- T, p) a/ ]4 ~: e: R) e: m( M" x! z2 o0 B4 b

yu 下午6:12

9 |3 T- ^5 x2 u" u: PBank. I& d0 Z1 j7 T0 _, e

8 b; g9 J% }" ]/ p9 n

qzheng 下午6:14

7 o: z% y: f& F3 F- n& F( A9 ~好漂亮的波形

* b- S! n2 D+ R; C, Z8 |$ m) N) U$ p0 u/ _: z4 P

24k纯丑 下午6:16' s0 k s: F/ L W3 R+ D9 C

好有钱的示波器

, Y5 v; d8 i8 D: o1 s

- d6 A$ P; d% z* E9 M0 I5 M/ ^

24k纯丑 下午6:17

5 ]- j( c7 m) n6 U4 G! @没有测试到末端会有比较大的影响9 Q, k% G& ]6 C( M* ^

! X: }9 t; e# M# u4 l

Andy Cao 下午6:183 ]* V9 E. K0 x3 k( r& j) r0 g

啥原因呢,为何2GH的WCK没问题,而1G的CK有问题?; |8 W% O# J. v4 N

! b6 ^" A* {& a6 ]! B

Andy Cao 下午6:18

, x4 F7 a D) {都是点对点

8 D( t. ]- r2 @. i- f

% _3 f7 \ Q8 a- D" A

Andy Cao 下午6:19! @1 I) @7 H* O1 c5 P/ ^

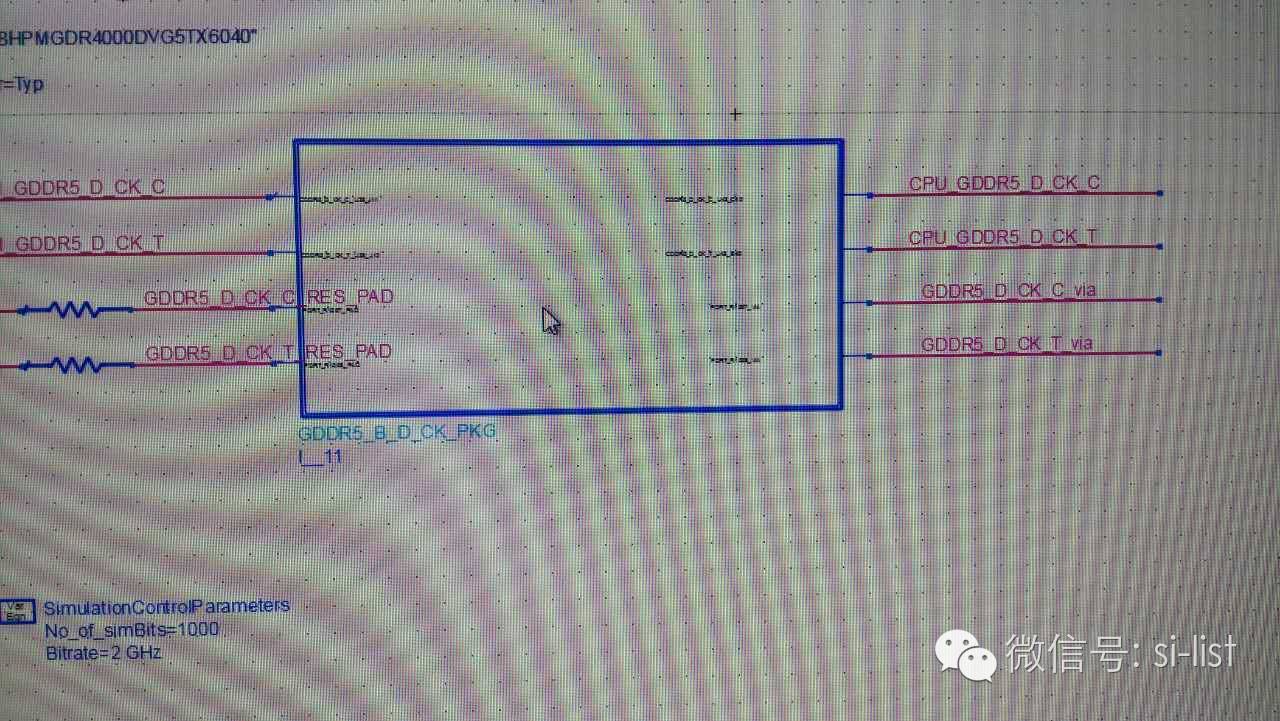

GDDR5 CK波形问题请教" ]! H* @$ N. x' j

BCM88370 到memory,memory末端60ohm电阻上拉到1.35V,60ohm电阻靠近memory放,在底层电阻pad+ W# {! \* C( N1 @

上抓的波形,其中memory贴在顶层,其中板厚140mil,CK波形出现非单调,而同组WCK波形是好的,只是WCK内部做了60欧姆端接,WCK在memory侧过孔上抓的波形,CK的走线和WCK类似,就多了外部60欧姆的上拉,且电阻pad离CK过孔仅30mil距离,这是什么原因啊,仿真弄了老半天都无法复现出测试波形单调问题

" I# |' p4 A; u9 C; H* ^% P2 s, Q( |; N7 ]) c z- n: Z: W

) B* N, l- I( H; n2 C

Andy Cao 下午6:19+ M: i, x4 g) O1 ^6 J3 c# }. f

再发一下ck测试波形* s# C1 _5 d' A8 Q; Y

/ S) T+ f" I+ i: m; D3 Y( P

24k纯丑 下午6:20. W# ^5 T4 A8 m8 O2 C; j

咋只有上升岩有?

6 z' Z0 \2 b ?: w8 Q% i

2 o6 |7 R0 B6 Q P+ f

24k纯丑 下午6:23

7 e c+ c. s! K. w. _! @这下好玩了

2 ^5 b! D- t. @4 T6 Z; h/ E/ V

& [* I1 c0 _5 u- H8 A- Q

qzheng 下午6:34

% W* I( M1 M9 _' z触发怎么设的9 i! s) [1 f" A6 E, P9 b

5 w7 H$ w% j4 n; q2 e

张吉权 下午6:54/ w6 o. o" N) w3 D

触发的设置会影响上升延的回沟么[疑问]9 r, z# l* r' _! v+ o- z

5 k2 w! z. v6 W" E& C( l+ X

qzheng 下午6:57

0 Y+ v' j7 F/ b: |, j+ {2 v; c% j不影响$ I' t, W& C3 S0 v* F" ]

+ Z$ c- W9 {1 o1 B* P" B, @* s

qzheng 下午6:58" m) \0 w9 X* K, G0 S

只是换个方式测波形,判断实际波形样子

* g. A: p" ]) z* T4 {0 M% t

8 {! r6 h4 S$ j9 v1 r5 J

郭永生 下午7:45" s3 f9 P3 G) N* L

@andy Cao 你把波形拉伸,看下是不是上升沿快过下降沿

/ l9 F7 u9 l: J. g" ^

$ w# b- i6 N- p. f; F3 ?4 ]

郭永生 下午7:47

, N4 t/ ~; N; y4 Z0 v+ H& }; f9 C% X1 l从波形顶部形状和底部形状来看,上升沿输出时,内阻较小,驱动较强劲,比下降沿冲的多一些

* T! o; }4 y$ J3 C

& z) s2 `' D( t5 b# B

邵鹏 下午7:48& P! ^6 w. [: t/ J8 ^

@Andy Cao 在源端加个22的串阻+ S& o/ c2 v; y5 I

- a4 j% q) A3 e7 a, D

郭永生 下午7:53

4 F0 W0 r H0 Z' Y回沟持续的时间,跟你测的位置还是大致温和的,从颗粒端反射回来的。下降沿其实也有影响,后半部分波形明显变缓了。3 G5 i4 \, ~! L6 s- {( i

6 P- \# C7 l* V

Andy Cao 下午7:54

. j7 {2 F& r) ~( p& z0 [好的明天试试,谢谢

$ d* J& A Z- F) y+ t, n" c4 Y" @4 ~7 t2 P7 j1 R4 r: w

邵鹏 下午7:55# R% c- D, b k. B7 c

或者像@汉普SI-郭永生 说的,降低驱动强度,GDDR的驱动强度是软件可调的

& G% Y+ ^. ]# T+ j+ c# j6 P4 Q1 [3 S

郭永生 下午7:568 r. B2 T; y+ d# @' E& v

能降低驱动强度,这个回沟就掩盖掉了,看能调整不8 H9 e& L& p( D, ]

. w; K9 g6 L2 x% g# H5 k

郭永生 下午7:58

1 B' f0 u. o& x0 T, s@Andy Cao 你可以对比一下,上升沿和下降沿初始一段的斜率,验证一下前面的推测,后半段时间已经受到影响,不要计入[微笑]

1 d: |. i! D+ @. z- U$ }3 r2 n& T, F: n8 Y8 e; z1 q; f

Andy Cao 下午8:187 d8 g6 T0 d4 m; V& z3 k

gddr5看不了测试代码

# J' P* @7 R4 F' K5 K7 gAndy Cao 下午8:20

% }! |5 b/ Q8 h% V# }" L 4 v3 @. m! t1 U0 G' I! Q9 |! j$ w

- m5 E$ ?0 o) g( c8 S/ N- r/ a

4 v3 @. m! t1 U0 G' I! Q9 |! j$ w

- m5 E$ ?0 o) g( c8 S/ N- r/ a Andy Cao 下午8:21

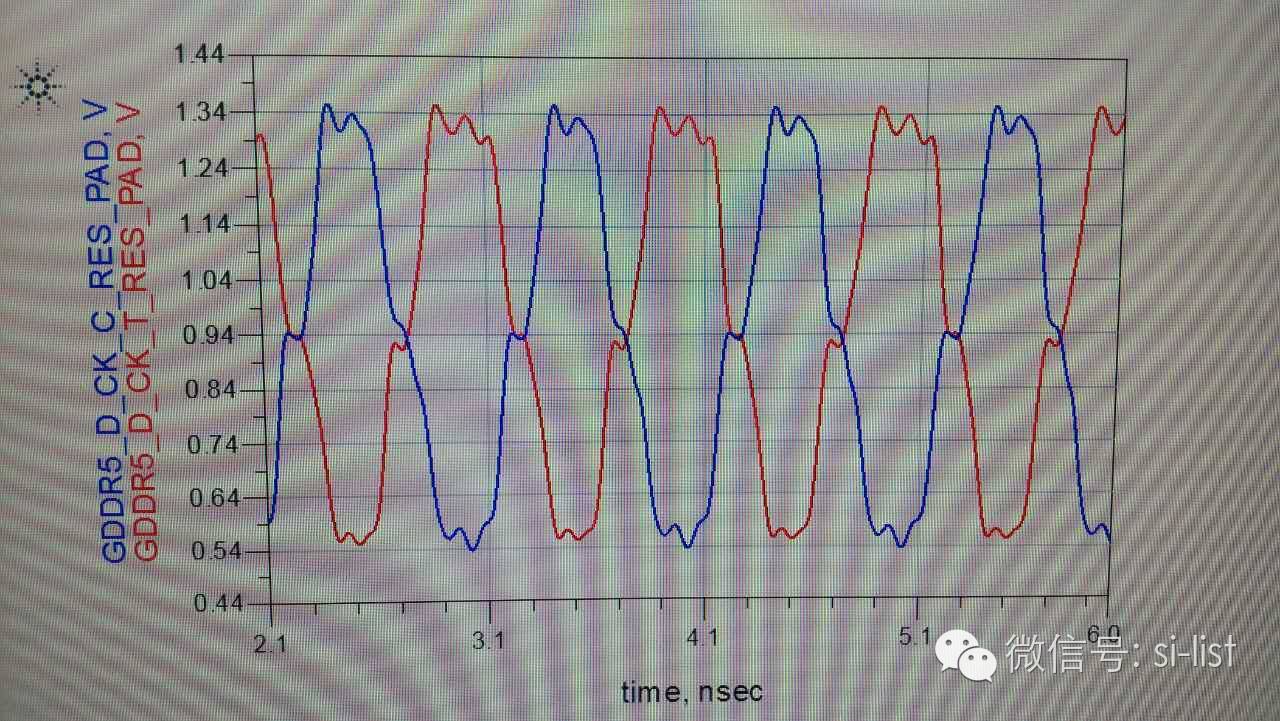

/ C. l& m" B7 A这是仿真的波形3 I4 f4 j# G, w# n

# x0 C* W5 v- w" g( ]# t

邵鹏 下午8:23

) f6 X8 Y3 O7 U3 _8 @@Andy Cao 方便把IBIS模型发给我吗? A& M" K9 w! `- |7 Q

! f6 @: L, }1 n9 ?! \! S' T2 N- z

敌敌畏 下午8:23

* I. F; d4 Y/ X+ z@Andy Cao 你的上升沿和下降沿时间不一样,下降缓慢0 w8 t( R, o' J6 L+ A

+ f f i M5 u3 u: Q, k4 t8 q

敌敌畏 下午8:23$ M% i. Y! l; T0 [2 E7 {8 A7 e* ~

缓慢的下降沿看不出台阶,上升沿快,台阶明显

% @2 T1 ~0 x) l# \ f# N2 r/ }, D- P% k

敌敌畏 下午8:24

3 |$ C: x4 [' V) `2 e' E在软件里,上拉比较小,下拉值比较大: P' U; a; J5 d1 M* n" ^

1 G6 r" o# U" t8 m

敌敌畏 下午8:25( j0 k8 `; q4 y& c& E

所以上升下降不一样,这是根据波形的猜测,验证猜测就是去看代码

/ y' W! L8 `5 ~

. R+ o# M0 N+ n/ R8 k

Andy Cao 下午8:26# y8 n( g% A$ J9 i: V; x1 b# ~

看不了代码呀8 n/ N, S5 W* S2 I& p8 o

$ `# k( w6 A4 p

敌敌畏 下午8:27

Q& h! ]3 C# S0 G% D所以,解释现象就是我说的1 b# R0 P2 }- ]4 a$ c; i. t

7 |# b; [9 f2 ]: H' ^

24k纯丑 下午8:284 V% p, P- p$ f7 k: s

目测两个沿差别不大,有这么明显的沟?$ f% f5 p. W" l' B

( u! {- `3 g/ j

Andy Cao 下午8:29

6 e' D% e' w# @& A7 n, m两边加了基板走线

L4 }! h C$ w, k$ q( z7 c/ Y8 N! y8 ~, L8 ~4 z

敌敌畏 下午8:30

4 }# p" q Z( K0 L6 [/ ^- ~) z' i7 [上升沿不到一百,下降目测在两百到三百$ L0 r1 i& S8 m/ I) G$ d9 i

9 Q, f: j/ `8 R1 @( z9 k

敌敌畏 下午8:32" j& x- H2 C+ I: O

用上拉34或者40的,下拉60的的模型试试仿下

5 V9 ]4 r9 ]( f( _4 a8 e" j

, @" i H" _$ ^+ O

郭永生 下午8:34

5 |! W+ w! N- ^, f@Andy Cao 你这仿真波形吻合的够可以的了,测试也会引入一些电容" a. o7 e6 V `2 K% V( |

; ]. |% G0 r H3 c( R+ U8 \

Andy Cao 下午8:34

5 \5 w8 j% S2 j问题是,我现在没法解释WCK波形为何没有台阶,而ck有

) _1 H, z* y8 G' n% g; r7 p0 ?, |4 j+ ~# Z- I9 Q

郭永生 下午8:36

" I+ ^5 P$ C0 e, {3 w5 Z- l前面提了,这个台阶是颗粒那边反射回来的,颗粒端应该没有

, o$ s, V+ l+ |& ^& v" o3 N+ r" H4 E/ c4 g' q* j

敌敌畏 下午8:360 y" z. h# w h1 F) h) D

基板模型是去参数的还是spice! V1 f" o7 p7 B& V, l& n1 W+ x6 I. a

7 I, v) N6 }( o2 r$ Q) x

Andy Cao 下午8:36

3 g x' W% ?1 ~) S. Sspice@敌敌畏 ) ^' W$ ?* Q ^

, V8 t' Q6 H* _( G- J

敌敌畏 下午8:36$ R1 l6 V" b& |/ G2 e

spice就对了,5 `* H9 j# k+ x

% f: _0 J5 C, F5 ~" I7 G

敌敌畏 下午8:37

! x) d2 e! Q- o. [; b! G看不到台阶,我现在也是这样的问题

6 `3 u/ f3 @7 E

& F8 x3 x$ o( K: J- V, Z- j

Andy Cao 下午8:37/ n5 v4 o' a y8 c' Y* Z

上图是仿真的wck波形5 d8 u8 A' ]3 b* w9 j0 Y

+ z$ a5 n( I, R' l- B

敌敌畏 下午8:38) O% v( A$ ~& `2 C

测试的呢

# W' z0 z7 n+ `( D$ Z* O! u* ?

! f3 c0 y4 a$ p7 |

Andy Cao 下午8:39

8 l" V6 s; ~1 ]6 K. M: A上图是测试的- t, f6 ~) {) ^; ^! ?5 n

8 S9 j; J) _& S( Q& q9 h1 F; O: J5 F

敌敌畏 下午8:390 X/ z/ A5 ?' o

搞不来了,我是用spice,仿真结果没台阶,和测试对的有问题,实际测试就是有台阶,

# |4 N2 v& b. q0 L. W% z- n6 y

* M) u1 |. Q q9 n9 N* S

敌敌畏 下午8:40; r; m) C) J. M' `5 K+ t( j) O

测试的有一点点台阶

( m# R4 R3 P3 o; t+ D3 g3 C# v& b7 d' R! B( g9 h& W" T

敌敌畏 下午8:40

& m0 @2 H+ _0 E6 f' @. F不明显

v( g# Y; L. i/ d7 O% v- |' N

+ V9 z5 d* w! @% s

敌敌畏 下午8:41+ U* e' _ M0 M. B" Y+ |

这个测试和仿真幅度貌似也不对1 g) K- @, E) _2 s( z, m

; f/ J5 X4 ~: q8 q! _" j

郭永生 下午8:428 z0 D& C7 z1 i1 x- B

@Andy Cao wck在内部端接,没信号反射回来,测试不受影响。CK外部端接,颗粒会反射,影响你测试。这个解释够合理吧[呲牙]( x5 w+ x, N% A) o7 \$ x- ]

5 Q7 A) f. ~( P

郭永生 下午8:43

: P1 v. u/ l9 D那个台阶100PS左右,反射长度上跟你距离颗粒长度吻合; E9 o K0 M: K5 g) o6 `' s& b+ W

/ \6 L% O. E1 s

敌敌畏 下午8:448 L: Q0 y9 }7 ~; e3 x2 _) s) S7 N

0 E7 i# f, j+ ?. ^9 [$ A2 e6 O@汉普SI-郭永生 我推翻你[呲牙],不反射,信号幅度会很小o+ b, F& H, ~$ p+ n l2 x

: W' f# o1 y/ E- g0 r8 g' ?

郭永生 下午8:47

- q8 N# t5 _9 t; N$ R0 m( }去掉接收端,加个电阻,看下幅值吧: A* v x5 W0 h0 @

( y' _% f# v' ^0 [

qzheng 下午8:480 H$ k) @( z7 u% {

还是看看模型吧,0 {+ y+ F/ M2 [9 d, G7 q6 b9 w

1 u6 C0 H! t9 r5 i( S4 [

qzheng 下午8:480 v, S+ g" A& }, p

把那几条线看看

9 N' d, I! a+ p9 ]4 G) O ~# s; O# d% a1 J' p, y, P7 H$ ^

qzheng 下午8:49! Y5 W! x' B6 d

如果没啥问题仿的就是正确的,模型里面没有的信息你也仿不出来7 A9 W$ \% |# N( Y1 F/ e

9 Q) N9 _) D: F" v4 a

Andy Cao 下午8:50

% Q, B3 C6 D5 [ d好的,谢谢大家7 b: ^ g/ T5 k! v2 Y2 F- _8 _1 \

. G- [" M) p" s+ p7 J7 H

郭永生 下午8:50

% p1 U1 _' t- O. ]- Z; b7 z( ~@Andy Cao 仿真去掉过孔和颗粒,你看看台阶还在不,验证很简单7 g2 m1 }; f, ]! H z2 q9 T2 Z

/ `# g6 W0 P" B; n! K

Andy Cao 下午8:51( q+ }- |- c& O+ _: T: j5 l& ]

过孔我是一起抽的

' w& T5 Q# N5 d. ]/ \4 D

4 [( P X0 z( q

Andy Cao 下午8:52

! y8 K& P% C$ x% N4 r2 b+ a 1 o3 F* }0 S3 w: Y

1 o3 F* }0 S3 w: Y