EDA365电子工程师网

标题: 说好不哭,直到电流“烧”红了过孔…… [打印本页]

作者: admin 时间: 2019-9-27 15:12

标题: 说好不哭,直到电流“烧”红了过孔……

微信公众号 | 高速先生( C+ i9 U( T5 U. R

文 | 姜杰# T9 e9 v! Q! ?" T' i

, p, {% W V% i, J/ b1 W# S' J* t. O4 t* ~6 X

不走寻常路的电流是PCB设计中的“刺头”,有时明明给它铺好了阳关道,它却偏偏要走独木桥,让人欲哭无泪。

4 U$ ?1 Q# e- \# P- \$ R1 k* _( s 就像高速先生之前遇到的一个案例,电源输出过孔排列的整整齐齐,虚位以待,电流偏偏舍近求远,就挑了几个你意想不到的过孔硬刚到底。

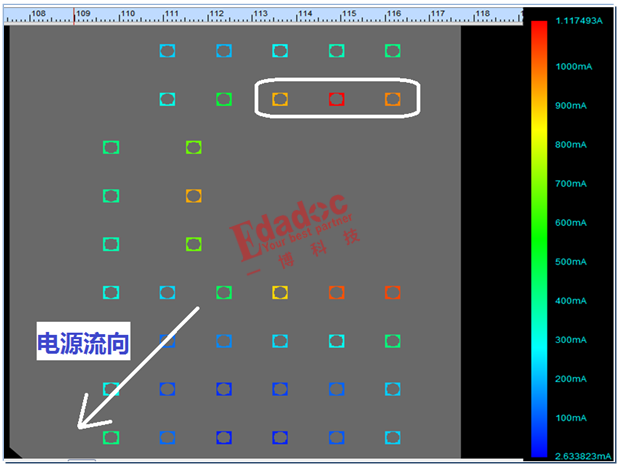

就像高速先生之前遇到的一个案例,电源输出过孔排列的整整齐齐,虚位以待,电流偏偏舍近求远,就挑了几个你意想不到的过孔硬刚到底。

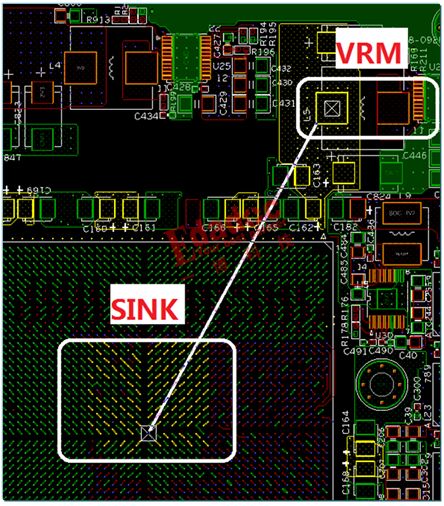

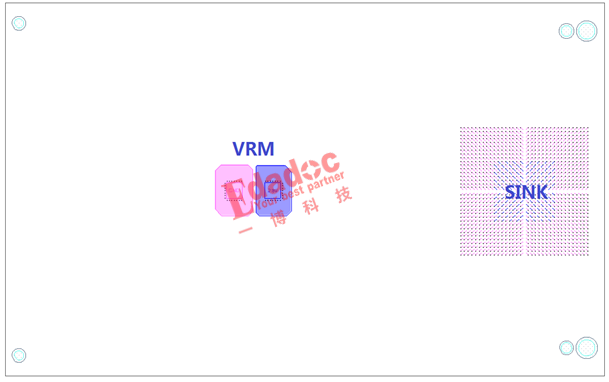

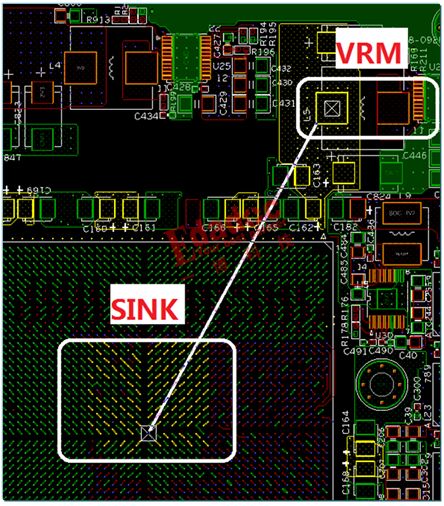

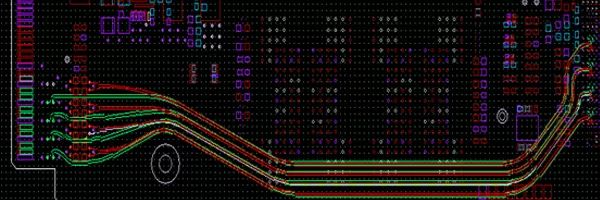

5 }4 a- W J4 o% }5 [) o s+ M* _ 供电模块VRM与用电端SINK的相对位置如下。

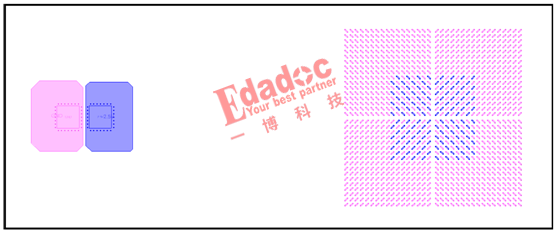

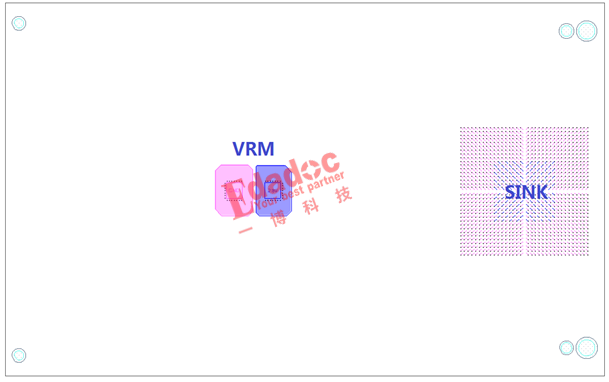

供电模块VRM与用电端SINK的相对位置如下。

2 U: D- a& @' ?2 I. q8 v0 @$ b$ y4 m; z9 K0 N

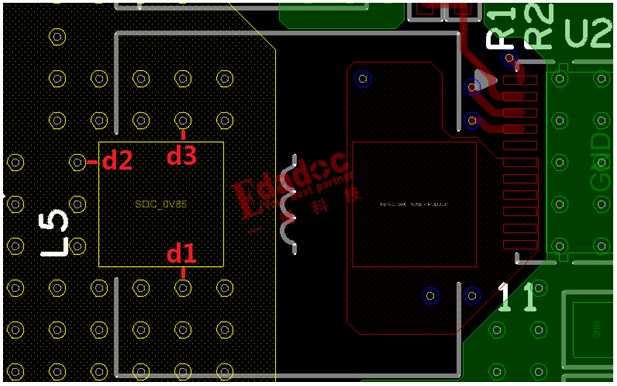

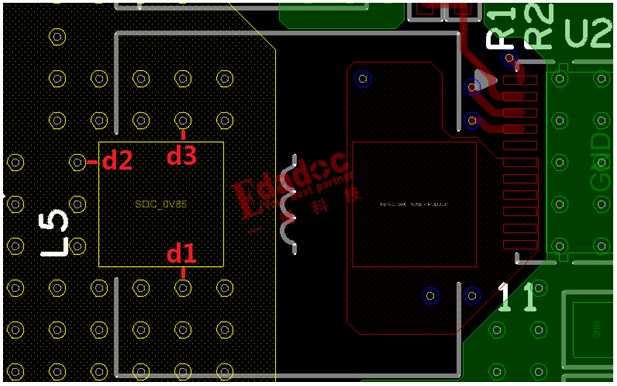

其中,VRM采用DC-DC开关电源,DC-DC外围电感L5电源输出管脚附近的过孔分布均匀,内圈过孔与管脚的间距d1=d2=d3(局部放大图如下)。+ ^* \) j, ^; W- |$ k- o& O. m: i

其中,VRM采用DC-DC开关电源,DC-DC外围电感L5电源输出管脚附近的过孔分布均匀,内圈过孔与管脚的间距d1=d2=d3(局部放大图如下)。+ ^* \) j, ^; W- |$ k- o& O. m: i

5 r! N, d8 x& o2 }5 @

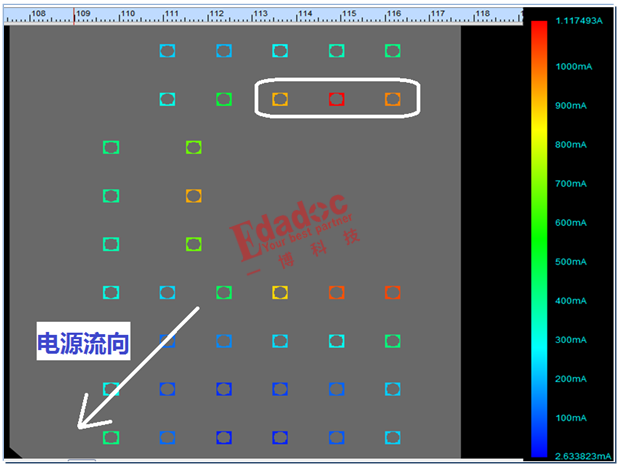

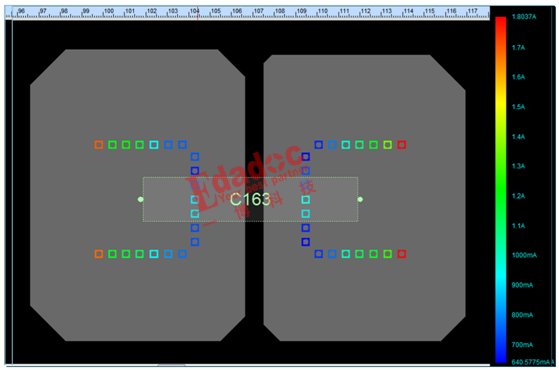

看起来似乎没啥毛病,按照预期,电流至少会在离L5电源输出管脚最近的内圈过孔上均匀分布。不过,再一想SINK端与VRM端的相对位置,有些朋友开始犯嘀咕了,电流都是喜欢走捷径(电阻较小的路径)的,那么,离SINK端更近的左下方的过孔通流会不会多点呢?高速先生一开始也是这么想,但是仿真的结果却让人大跌眼镜:过孔电流分布图显示,在电流流向的反方向(白色方框区域),有几个过孔通流较大,这是怎么回事?!% ]- h a9 K# U) m

看起来似乎没啥毛病,按照预期,电流至少会在离L5电源输出管脚最近的内圈过孔上均匀分布。不过,再一想SINK端与VRM端的相对位置,有些朋友开始犯嘀咕了,电流都是喜欢走捷径(电阻较小的路径)的,那么,离SINK端更近的左下方的过孔通流会不会多点呢?高速先生一开始也是这么想,但是仿真的结果却让人大跌眼镜:过孔电流分布图显示,在电流流向的反方向(白色方框区域),有几个过孔通流较大,这是怎么回事?!% ]- h a9 K# U) m

9 z& t- A* Q! w" n' j

打破砂锅问到底是高速先生的一贯风格。通过仔细分析过孔载流,发现过孔通流除了与电源输出管脚的间距有关系,似乎与过孔阵列的缺口方向也存在某种神秘的关联。

打破砂锅问到底是高速先生的一贯风格。通过仔细分析过孔载流,发现过孔通流除了与电源输出管脚的间距有关系,似乎与过孔阵列的缺口方向也存在某种神秘的关联。

* f. u! ~$ a: @& s/ x1 Y$ d3 ~, _$ T2 s: m. G( k8 ]' u" [

0 C% w: K# m4 G$ Z8 X( g* w

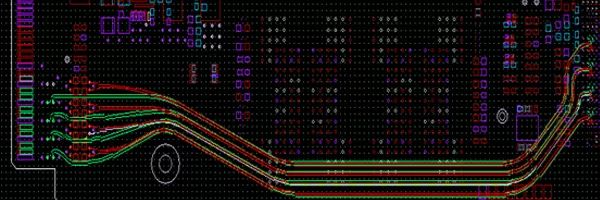

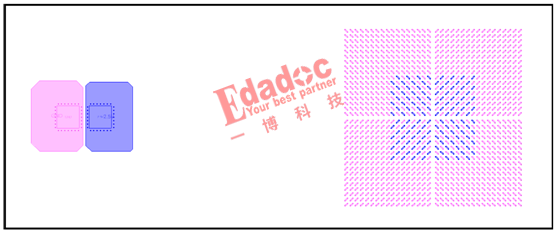

J6 n8 A) f5 n8 o/ o3 x大胆假设,小心求证,困难看淡,说干就干。先把模型简化,删除板上其它器件和走线,保留内层电源、地平面的连接,同时,将VRM用一端电源输出、另一端接地的电容代替,调整VRM与SINK的相对位置。简化后的模型如下。

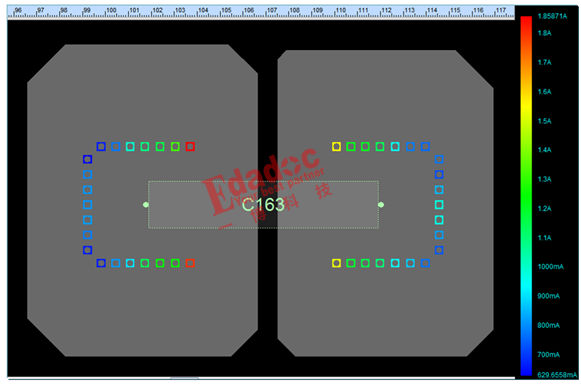

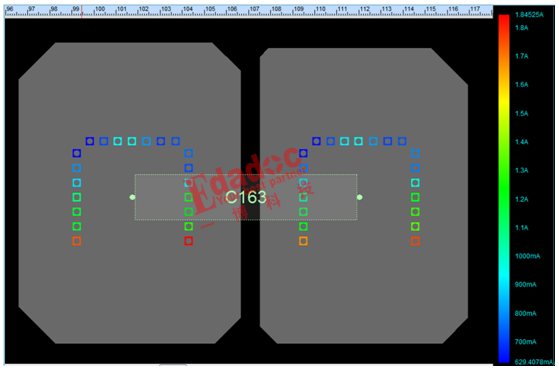

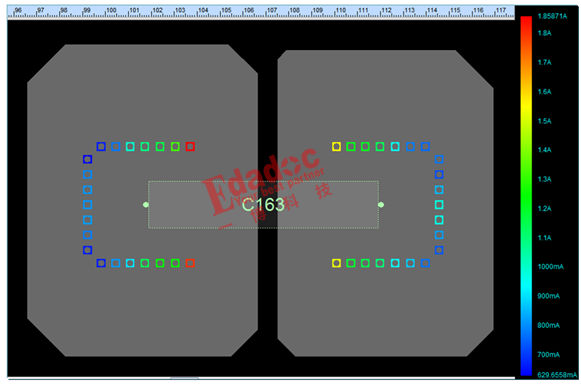

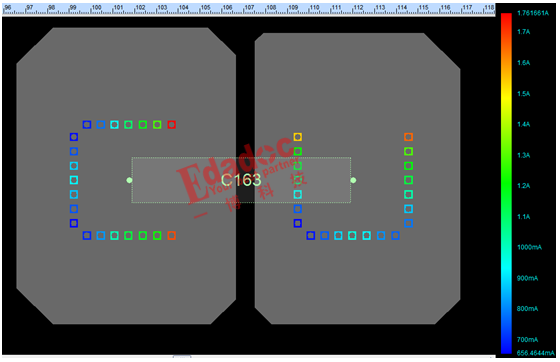

7 o* k; E: t. y: u+ R 简化模型的VRM端过孔电流分布已初露端倪,似乎能看出点趋势来了。

简化模型的VRM端过孔电流分布已初露端倪,似乎能看出点趋势来了。

: M6 a# w6 |7 [. y* q8 ~; o) ^; ^) t) M( o) o, D$ o

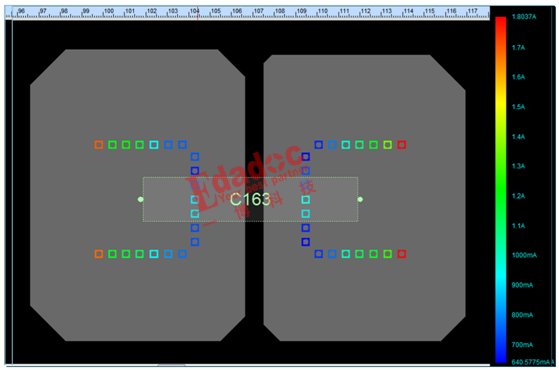

为了能进一步说明问题,我们继续调整过孔阵列的缺口方向,比较过孔载流的情况。: ]& t5 b; k. L& p# ]2 ~

为了能进一步说明问题,我们继续调整过孔阵列的缺口方向,比较过孔载流的情况。: ]& t5 b; k. L& p# ]2 ~

; B% z) l! P2 u0 ^% H% j: G+ g

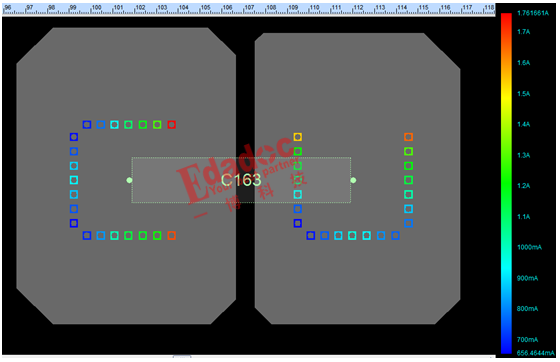

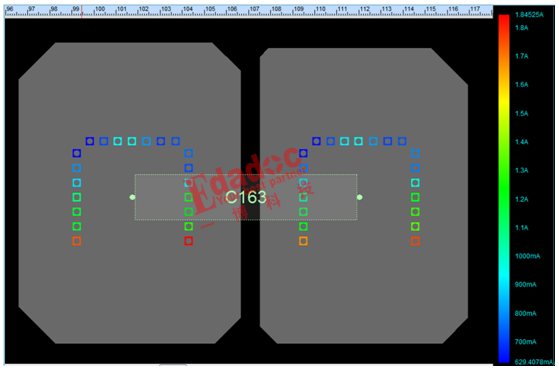

只看阵列缺口对称时的情况似乎还不够全面,那就再看看不对称时的载流。

只看阵列缺口对称时的情况似乎还不够全面,那就再看看不对称时的载流。

3 W& G2 n! _1 y; m$ H7 Q5 ]% J! j+ |7 p" l

想必各位已经看出规律了:在电源输出过孔与管脚间距相同的情况下,最靠近阵列缺口的过孔载流最大。为什么会出现这种现象呢?7 R+ j0 o4 X$ ^$ ?; r) ~ Q

想必各位已经看出规律了:在电源输出过孔与管脚间距相同的情况下,最靠近阵列缺口的过孔载流最大。为什么会出现这种现象呢?7 R+ j0 o4 X$ ^$ ?; r) ~ Q

/ |) v" \1 c. X, X6 N# i. u

: s s F8 Z% e- b! ^

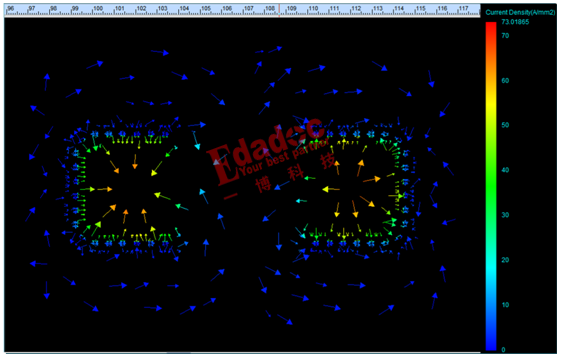

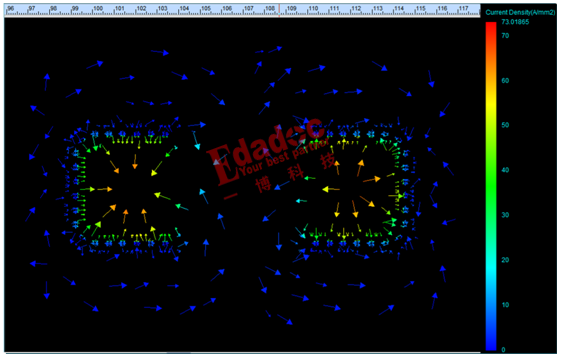

8 b: c* h0 {( ~ ]" u不妨再来看看电流密度图。以左侧的电源输出管脚为例,一开始电流以管脚为中心向四周均匀发散,对于有过孔分布的三个方向,电流会迅速找到最近的过孔,流向内层电源平面。而从过孔阵列缺口溜出来一部分电流,遭遇大概是这样的:出发时扫眼一看,一马平川,前方全是铜皮,没有过孔挡路,好嗨哟,跑着跑着发现没路了,不知谁喊了一嗓子:“此路不通,拐啦拐啦!”于是,逃窜出来的大部分电流又猛打方向,掉头钻进了离缺口最近的过孔。

7 G& L4 n3 ], [& O4 y6 ? 这么一折腾,出现阵列缺口附近过孔载流最大的现象也就不足为奇了。& I: R6 h7 Z5 z: \5 G

这么一折腾,出现阵列缺口附近过孔载流最大的现象也就不足为奇了。& I: R6 h7 Z5 z: \5 G

/ a5 h& {1 S' j3 f S P8 a1 |8 _& w$ N

2 n# \- v5 y! z$ v- G8 K: b

2 n# \- v5 y! z$ v- G8 K: b

: d1 r3 [( I5 E+ W— end —

# T( i$ k* z( m& l& P, W* A

% r* i* y3 v4 _, u! L3 d本期提问

6 J* u0 L; t' i2 `

% d" G- L) b) o# R% Z, i L保持同样的过孔间距,阵列缺口补上之后VRM端载流最大的过孔会出现在哪个位置呢?3 ~8 m% J/ @. k7 X( |* d

+ [% X7 [. A; J( h& K1 s

1 ]* P, F* K7 ]

* R& w3 }) m) n/ J

$ t. v8 b# N6 z6 H! r2 {8 L

& M; s, O- u5 T- \& X

! ^, y% B2 t- Q3 i7 p" Z# k& n5 s: h6 W! X) X1 ^) |

1 @6 y' M ~; L! s' v4 M————你可能错过的往期干货————0 q- R+ @4 `% J5 o2 ~9 o1 U: _, Y8 P

# u8 |, a3 s/ C/ W2 U

没空间啦,我能不往板边走线吗!

没空间啦,我能不往板边走线吗!

; i3 i- b" R8 O1 _ 宝藏文,高速先生所有原创技术文章,戳戳戳!. q- M, _) h9 _% F6 w; e

宝藏文,高速先生所有原创技术文章,戳戳戳!. q- M, _) h9 _% F6 w; e

& l8 T. m" \4 u; D6 \9 Y

b: ^* C. [9 |$ V! m回复数字获取往期文章。(向上滑阅览)

( F* C* V9 Y h' T0 Y. m. y7 @. g" u

% j& s/ G3 N/ ?; f4 N- c* O回复36→高速串行之S参数系列

, B( m# E; R2 X5 ^ _7 K6 Q& q, S回复35→高速串行之编码系列

9 f, w( X( s5 q; }回复34→高速串行之S参数-连接器系列

. s$ H- p* J& e9 M回复33→高速串行简史系列6 Z) h2 p0 L: C- W0 O

回复32→电源系列(下)

* ~5 Z! K6 }" g9 G* ^9 M: \5 _回复31→电源系列(上)9 f- @, T: i6 k/ \ Q. p' B

回复30→DDR系列(下)# M3 h4 ]0 o a) A$ x2 U3 E

回复29→DDR系列(上)) `5 @3 ?4 {" ^* C4 e. D! [ {

回复28→层叠系列(下)' b* E5 r& r5 @: X6 }$ U% X( y

回复27→层叠系列(上)* L9 c5 b( J9 `) A& e) A- u6 @

回复26→拓扑和端接系列(下)" w l0 r6 B/ C" L* E

回复25→拓扑和端接系列(上)

6 k% i* s2 y3 Y( _% G1 n" e回复24→反射详解系列文章

H& }& {7 S; q. b回复23→阻抗系列(下)4 T; P) Q) o8 ~

回复22→阻抗系列(中)

8 q' Y5 g4 y5 W+ A" x. _回复21→阻抗系列(上), O$ _# \+ [6 O& U

回复20→绕线与时序5 ^9 C, Y5 T0 ]8 `# k+ P

回复19→SERDES与CDR系列

0 l4 l; G' n) \5 B回复18→既等长,为何不等时系列 f. y' p( e6 ?; u

回复17→cadence等长处理&规则设置

' A: ]' o0 x3 J: Z3 @回复16→DDR时序学习笔记系列2 k$ _' A4 c, Y: z% n& b

回复15→串行系列

: ?, i6 X' B9 u9 r- ?& c回复14→DDR信号完整性仿真介绍系列

! i: N" d+ L. H8 b/ B; D回复13→PCB设计技巧分享一二+ J6 W0 p+ a1 V; X5 R

回复12→高速设计三座大山

; }# P4 {) |. d: w回复11→PCB设计十大误区-绕不完的等长系列

; U, h, Q9 k6 p, g回复10→PCB设计十大误区三: H. b$ H, H, \, a! A* ]) L

回复09→DDRX系列$ I) ?( Z& J) [. e1 ~

回复08→高速串行系列: ?5 U3 {, q g& {

回复07→设计先生之回流设计系列* v$ V" x* M9 V. ^ x. Y4 n

回复06→略谈Allegro Pcb Design 小技巧

6 A/ L- Y2 y' `& @回复05→PCB设计十大误区一二

0 {) B3 I7 j" `& X \回复04→微带线系列* `7 A/ T7 n) q7 w5 U

回复03→抽丝剥茧系列

k, v& [3 J! h* h回复02→串扰探秘系列

" }; z N- S9 E. V) n回复01→案例分享系列

4 @" | ?( J" r* |1 Q5 j9 x9 D

' Q6 V' C' \& k) ^+ E( D5 k$ H0 s

觉得内容还不错的话,给我点个“在看”呗' ?: }' X, O* s, f A2 e" @

3 x& g" O. r0 B& J; J f, t$ w

| 欢迎光临 EDA365电子工程师网 (http://bbs.elecnest.cn/) |

Powered by Discuz! X3.2 |

就像高速先生之前遇到的一个案例,电源输出过孔排列的整整齐齐,虚位以待,电流偏偏舍近求远,就挑了几个你意想不到的过孔硬刚到底。

就像高速先生之前遇到的一个案例,电源输出过孔排列的整整齐齐,虚位以待,电流偏偏舍近求远,就挑了几个你意想不到的过孔硬刚到底。 供电模块VRM与用电端SINK的相对位置如下。

供电模块VRM与用电端SINK的相对位置如下。 其中,VRM采用DC-DC开关电源,DC-DC外围电感L5电源输出管脚附近的过孔分布均匀,内圈过孔与管脚的间距d1=d2=d3(局部放大图如下)。+ ^* \) j, ^; W- |$ k- o& O. m: i

其中,VRM采用DC-DC开关电源,DC-DC外围电感L5电源输出管脚附近的过孔分布均匀,内圈过孔与管脚的间距d1=d2=d3(局部放大图如下)。+ ^* \) j, ^; W- |$ k- o& O. m: i 看起来似乎没啥毛病,按照预期,电流至少会在离L5电源输出管脚最近的内圈过孔上均匀分布。不过,再一想SINK端与VRM端的相对位置,有些朋友开始犯嘀咕了,电流都是喜欢走捷径(电阻较小的路径)的,那么,离SINK端更近的左下方的过孔通流会不会多点呢?高速先生一开始也是这么想,但是仿真的结果却让人大跌眼镜:过孔电流分布图显示,在电流流向的反方向(白色方框区域),有几个过孔通流较大,这是怎么回事?!% ]- h a9 K# U) m

看起来似乎没啥毛病,按照预期,电流至少会在离L5电源输出管脚最近的内圈过孔上均匀分布。不过,再一想SINK端与VRM端的相对位置,有些朋友开始犯嘀咕了,电流都是喜欢走捷径(电阻较小的路径)的,那么,离SINK端更近的左下方的过孔通流会不会多点呢?高速先生一开始也是这么想,但是仿真的结果却让人大跌眼镜:过孔电流分布图显示,在电流流向的反方向(白色方框区域),有几个过孔通流较大,这是怎么回事?!% ]- h a9 K# U) m 打破砂锅问到底是高速先生的一贯风格。通过仔细分析过孔载流,发现过孔通流除了与电源输出管脚的间距有关系,似乎与过孔阵列的缺口方向也存在某种神秘的关联。

打破砂锅问到底是高速先生的一贯风格。通过仔细分析过孔载流,发现过孔通流除了与电源输出管脚的间距有关系,似乎与过孔阵列的缺口方向也存在某种神秘的关联。 简化模型的VRM端过孔电流分布已初露端倪,似乎能看出点趋势来了。

简化模型的VRM端过孔电流分布已初露端倪,似乎能看出点趋势来了。 为了能进一步说明问题,我们继续调整过孔阵列的缺口方向,比较过孔载流的情况。: ]& t5 b; k. L& p# ]2 ~

为了能进一步说明问题,我们继续调整过孔阵列的缺口方向,比较过孔载流的情况。: ]& t5 b; k. L& p# ]2 ~

只看阵列缺口对称时的情况似乎还不够全面,那就再看看不对称时的载流。

只看阵列缺口对称时的情况似乎还不够全面,那就再看看不对称时的载流。 想必各位已经看出规律了:在电源输出过孔与管脚间距相同的情况下,最靠近阵列缺口的过孔载流最大。为什么会出现这种现象呢?7 R+ j0 o4 X$ ^$ ?; r) ~ Q

想必各位已经看出规律了:在电源输出过孔与管脚间距相同的情况下,最靠近阵列缺口的过孔载流最大。为什么会出现这种现象呢?7 R+ j0 o4 X$ ^$ ?; r) ~ Q 这么一折腾,出现阵列缺口附近过孔载流最大的现象也就不足为奇了。& I: R6 h7 Z5 z: \5 G

这么一折腾,出现阵列缺口附近过孔载流最大的现象也就不足为奇了。& I: R6 h7 Z5 z: \5 G 2 n# \- v5 y! z$ v- G8 K: b

2 n# \- v5 y! z$ v- G8 K: b

没空间啦,我能不往板边走线吗!

没空间啦,我能不往板边走线吗! 宝藏文,高速先生所有原创技术文章,戳戳戳!. q- M, _) h9 _% F6 w; e

宝藏文,高速先生所有原创技术文章,戳戳戳!. q- M, _) h9 _% F6 w; e