EDA365电子工程师网

标题: 优化封装以满足SerDes应用键合线封装规范 [打印本页]

作者: admin 时间: 2019-9-27 15:51

标题: 优化封装以满足SerDes应用键合线封装规范

对于10Gbps及以上数据速率的SerDes,每个数据位的单位间隔是随着近 20~30ps的信号上升/下降时间而缩短的。选择合适的封装互连结构,有效地传输这些信号已成为最大限度减少信号完整性问题的重要考虑因素,如串扰、阻抗不连续性等。对于低成本应用,键合线封装是替代相对高端的倒装芯片封装的首选方案,但它缺乏执行大I/O数、控制阻抗及为芯片提供有效电源的设计灵活性。

0 p5 v y0 Z+ F6 J+ E" z 本文将讨论通过优化封装内的阻抗不连续性和改善其回波损耗性能,以满足10Gbps SerDes键合线封装规范。

6 D& `! A% [( A: J 差分阻抗

1 g" _( w; i; b* l' y% K 一个典型的SerDes通道包含使用两个单独互连结构的互补信号发射器和接收器之间的信息交换。两个端点之间的物理层包括一个连接到子卡的键合线封装或倒装芯片封装的发射器件。子卡通过一个连接器插在背板上。背板上的路由通过插入的子卡连接到一个或一组连接器。采用键合线或倒装芯片封装的接收芯片也位于这些子卡上。- s1 H$ R6 q( ~3 A) |* S4 ]

如果设计不合适,一个通道中的这些多重转换将会影响信号完整性性能。在10Gbps及以上,通过最大限度地减少阻抗不连续性,得到适合的互连设计已成为提高系统性能的一个重要的考虑因素。由于封装内有许多不连续区,该收发器封装在提高回波损耗性能方面存在一个重要瓶颈。! X5 A5 l- @5 h o- z( K& B0 W9 V$ d$ }, a

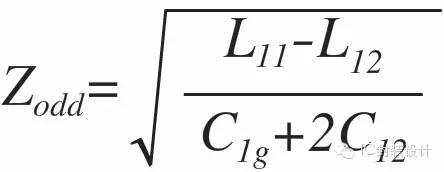

SerDes通道设计通常为100Ω差分阻抗。由于差分信号采用奇模传播,差分对的每线奇模阻抗都必须是50Ω。差分对的每线信号都需要有50Ω的恒阻抗,以尽量减少回波损耗,最大限度地提高性能。

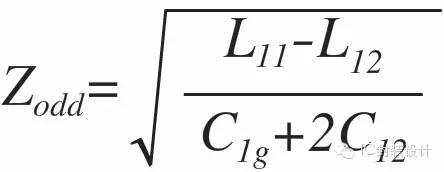

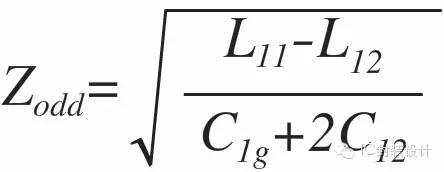

3 m/ c- i3 q# S) m9 k$ P0 q 损耗较少的系统的奇模阻抗定义为: h$ z, `' ^9 K' Y

4 f# H7 G/ u r, }% P. ~; k+ T

4 f# H7 G/ u r, }% P. ~; k+ T

为了优化每线阻抗,所有四个分量都需要平衡,以达到50Ω阻抗。对于差分对,在每一个单端信号传送一对信号,L12和C12分量都不存在,Zodd是自L/C的平方根。6 y) Z- r0 y" T* r/ c

1 @' {! v. O4 P, n$ w

5 N8 z1 n; R6 a9 B 一次预处理封装1 B, L( J6 L9 x" d& Z" H; S1 j

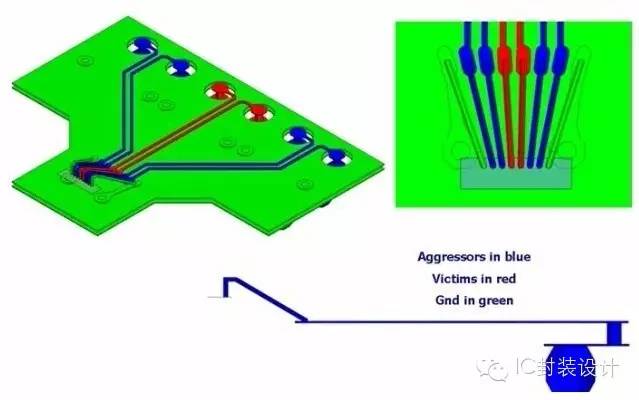

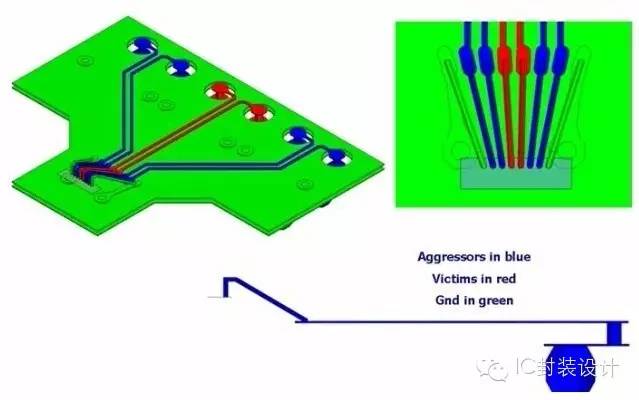

有三个差分对的典型的键合线封装的截面如图1所示。发射器对以蓝色显示,居中的接收器对为红色。该封装基板是一个传统的4层基板,顶层有微带印制线,第二层和第三层是电源/接地,焊球在最后一层。这个一次预处理设计的优化可以满足基频数据速率下-15dB和一次谐波频率数据速率下-10dB的回波损耗规范。 C3 q; @# |# B' Z( O+ h

+ {2 R: A1 B; K, J* ^6 c7 S- B$ H

+ {2 R: A1 B; K, J* ^6 c7 S- B$ H

图1 一次预处理封装

- l+ J! U6 G* K7 R. ^4 V9 ~2 g+ h

g; ~6 }% S( y! L3 d* \

一个典型的键合线封装可以分成三个阻抗区;主要是感应键合线区、印制线路由传输线区和电容焊球/通孔区。+ r5 @& v& [! R9 x

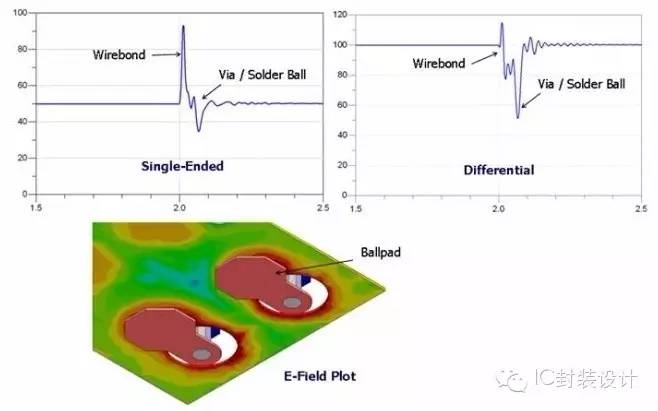

; Y3 \5 i/ l$ p0 H1 M) t L0 V 单端和差分TDR响应

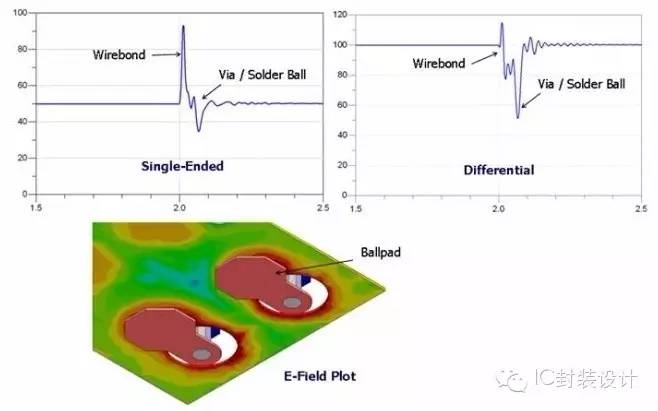

% A% y2 ^( ~& Y( ?9 M 时域反射计(TDR)技术用来监控从芯片到PCB的信号遇到的阻抗。图2显示了作为一个单端信号,也可作为一个差分信号驱动的差分对中的每线TDR响应。图1中只有一个对用于TDR分析,而其他对接地,忽略串扰对TDR响应的影响。 Z5 k- K( X' e

单端TDR曲线显示了主要电感、后面跟着一小段传输线的高阻抗键合线区互连结构,其后面是电容、低阻抗通孔和焊球区。由于在差分对键合线区有强大的相互感耦合,当相同的结构进行差分驱动时,电感键合线尖峰不太明显。由于差分设置的互电容增加了一倍,电容dip显着恶化。消除来自通孔/焊球区的额外电容是实现100Ω 差分阻抗的关键。图2 还显示了焊点区的电场(E-field)曲线,以及集中在焊点上的强电场。) ^# ] R8 D0 A+ _+ |

$ O$ q1 q! ^, ]/ [

$ O$ q1 q! ^, ]/ [

/ n1 t2 e" X$ c图2 单端和差分TDR曲线

9 t7 E9 e2 O; H8 q* t3 i: `" c# V

1 e2 T \8 j+ Q3 h. S# V, N

& M# m; T: [, z: r 提高TDR 性能$ z Y" C% y/ y3 z9 Z& d# X

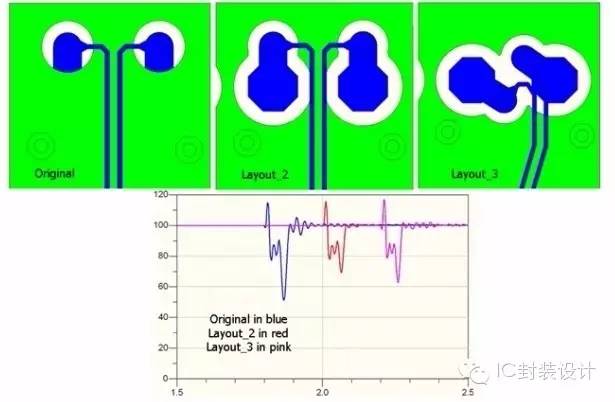

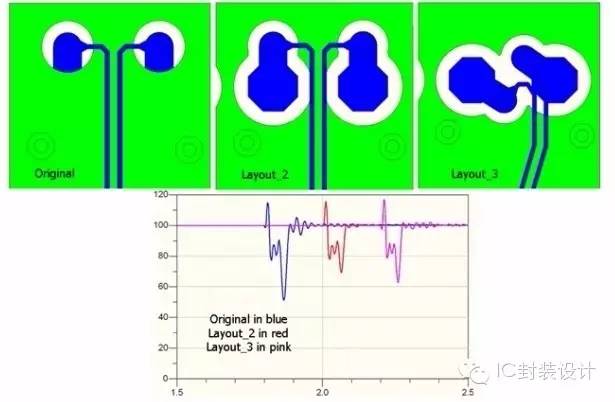

图3显示了原来布局的变化(在焊点/通孔区)及其对差分TDR性能的影响。这些略大于焊点的孔是在焊点上的金属层Layout_2上实现的。原有布局的电容dip现在大约小到20Ω。另一个来自Layout_2的试图修改的部分是从松散耦合到紧耦合来改变通孔定位,如Layout_3所示。紧耦合通孔旨在提高差分对的串扰性能。它已在另一项研究中得到证明,串扰性能的改善微乎其微,这里不介绍这项研究的其他内容。Layout_3的粉色波形显示,由于额外两个通孔之间的电容耦合,电容dip略差。

5 s/ c3 |" N* O0 ]3 S8 w4 X 7 E7 q. z1 s6 y) z7 N# P4 v: Q

7 E7 q. z1 s6 y) z7 N# P4 v: Q

图3 三种布局的差分TDR响应

6 O, h# \' q6 U$ @9 r2 ~* T6 z, Z* @5 m7 V

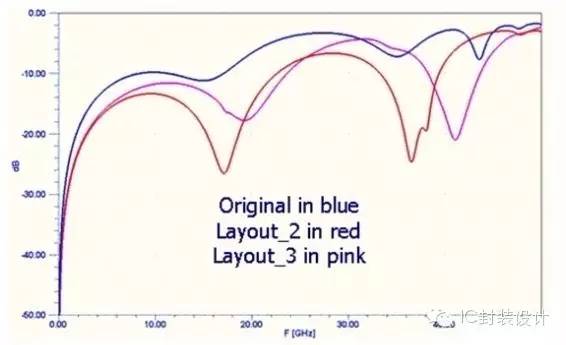

& e! z' U2 R! a( t 回波损耗性能的影响

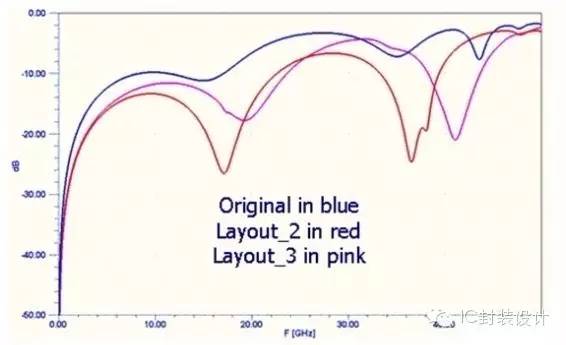

& o$ h% x( W" _1 Y" N, } 图4显示了每次修改后回波损耗性能的影响。Layout_3原始布局的整体回波损耗最差。Layout_2 显示出最佳的整体回波损耗,它直接关系到其TDR性能。5 Q6 C' l6 c2 x6 k: K+ ?8 l

在5GHz下Layout_2的回波损耗为-16dB,而在10GHz下为-14dB,可以轻易满足基频为-15dB的规范,以及10Gbps SerDes接口一次谐波频率-10dB的规范。

0 J8 e- X, N& Q# |+ D3 o & B$ X3 ` i0 ]- y( l/ C

& B$ X3 ` i0 ]- y( l/ C

8 T1 `/ b8 \3 q& _图4 每次修改后回波损耗性能的影响

" n5 S: x) }* e) b& h

0 Y* c8 C. Y3 [: J

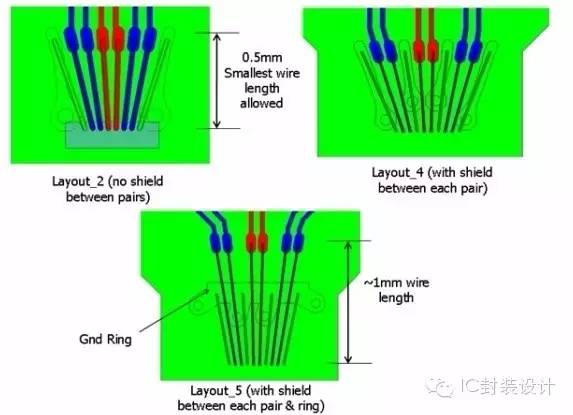

. N2 h+ A! U$ Y7 q 片芯焊点环布局的影响

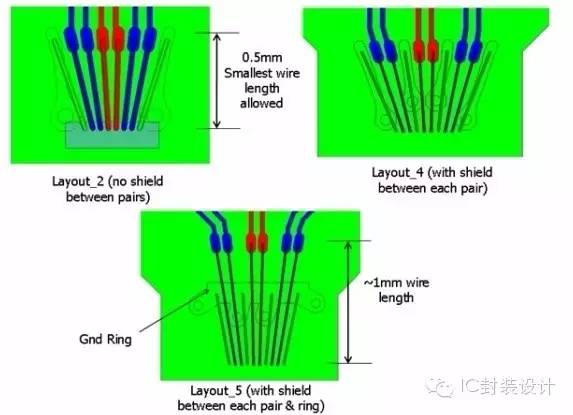

. Z$ D- J/ `3 [8 D( x6 J5 E U 为了尽量减少对间串扰,理想的是用回波焊点隔开芯片上的每个差分对。当边缘速率在20-30ps级时,由于干扰源-受扰者串扰,可能严重恶化接收器性能,这一点至关重要。要保持通孔和焊球焊点区与Layout_2一致,图5给出了与芯片封装键合线连接相关的两个额外的封装布局变化。3 m7 l4 h* c$ H

0 \3 @, ?3 _4 c5 E- A

0 \3 @, ?3 _4 c5 E- A

图5 片芯焊点环和键合线布局变化

& q6 {$ i- a. K: c1 d5 Q4 u! I5 j' ?9 X

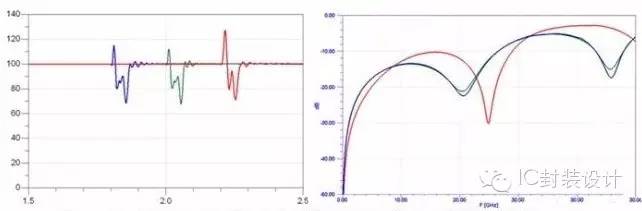

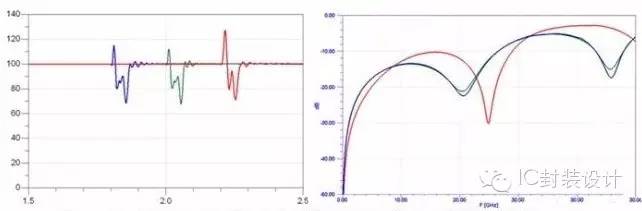

: l; Z$ C5 r/ W2 F1 G! G6 m 图6显示了三个布局的差分TDR和回波损耗性能。蓝色的Layout_2响应与前边的图一样。由于相对较小的间断电感,但其频域影响不变,Layout_4的TDR性能稍好。Layout_5 TDR响应显示,由于相对于其他两个布局的键合线,感应尖峰几乎为2倍。图6也显示了长键合线对回波损耗性能恶化的直接影响。* K+ M: [. ^! D" _4 {' o& a T2 ]: L

; r2 K- |" P5 ]) b, _8 b& [! b6 _0 ?

; r2 K- |" P5 ]) b, _8 b& [! b6 _0 ?

图6 由于 片芯焊点环和键合线布局的改变影响了TDR和回波损耗性能

3 k/ w* a, C3 \. O

( g! C2 ]& u; t5 C6 V8 @' w# C: z

7 j, _- q x' {6 R1 O' C9 a6 l 本文小结

# u F j8 M( C, J$ v" j 本文解释了键合线封装中的两个主要不连续区;讨论了10Gbps数据速率范围优化键合线封装布局的快速技术;也显示了键合线长度对回波损耗性能恶化的影响。, ~$ m: F% d) e8 T. ?$ j- e2 |$ D

* y* _' e8 T* j$ \ R% ?" P

| 欢迎光临 EDA365电子工程师网 (http://bbs.elecnest.cn/) |

Powered by Discuz! X3.2 |

4 f# H7 G/ u r, }% P. ~; k+ T

4 f# H7 G/ u r, }% P. ~; k+ T 4 f# H7 G/ u r, }% P. ~; k+ T

4 f# H7 G/ u r, }% P. ~; k+ T

$ O$ q1 q! ^, ]/ [

$ O$ q1 q! ^, ]/ [