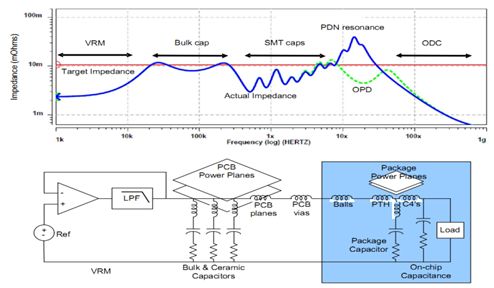

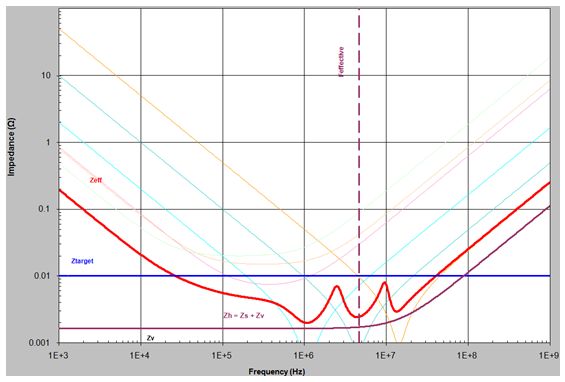

芯片在开关时产生的高频开关噪声将沿着电源平面传播。去耦电容可以给高频噪声提供一个低阻抗的回路路径,就近回流到地平面。实际板级PDN管控频段一般为100KHz到20MHz。100KHz以下频段噪声VRM内部就能管控。20MHz以上的频段,受电容寄生参数影响,板级的管控成本高,效率低。针对更高频段的噪声,芯片厂商会在封装内部和DIE内部集成相应的去耦电容进行去耦。8 F3 G8 ] B; v0 `; h. o

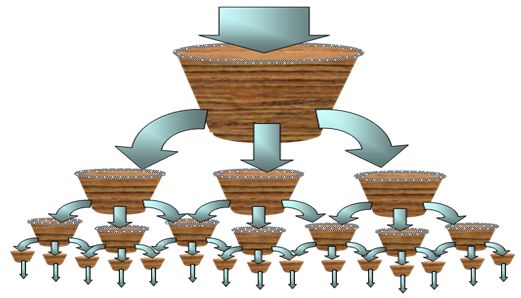

芯片在开关时产生的高频开关噪声将沿着电源平面传播。去耦电容可以给高频噪声提供一个低阻抗的回路路径,就近回流到地平面。实际板级PDN管控频段一般为100KHz到20MHz。100KHz以下频段噪声VRM内部就能管控。20MHz以上的频段,受电容寄生参数影响,板级的管控成本高,效率低。针对更高频段的噪声,芯片厂商会在封装内部和DIE内部集成相应的去耦电容进行去耦。8 F3 G8 ] B; v0 `; h. o 例如一个1V/10A电源我们常见的电容配置是, 330U 1个, 100U 2个, 47U 4个,10U 8个 ,1U 16个 ,0.1U 32个。其中300U/ 100U/ 47U/10U电容管控100KHz到1MHz频段噪声,1U/0.1U/电容管控1MHz到20MHz噪声。' u1 V9 E: l* T. r9 V2 z, k0 S

例如一个1V/10A电源我们常见的电容配置是, 330U 1个, 100U 2个, 47U 4个,10U 8个 ,1U 16个 ,0.1U 32个。其中300U/ 100U/ 47U/10U电容管控100KHz到1MHz频段噪声,1U/0.1U/电容管控1MHz到20MHz噪声。' u1 V9 E: l* T. r9 V2 z, k0 S

查看我的积分,回复关键词“2019积分”;: d- b. Z5 l2 j4 U+ J+ E& [; U

查看我的积分,回复关键词“2019积分”;: d- b. Z5 l2 j4 U+ J+ E& [; U| 欢迎光临 EDA365电子工程师网 (http://bbs.elecnest.cn/) | Powered by Discuz! X3.2 |