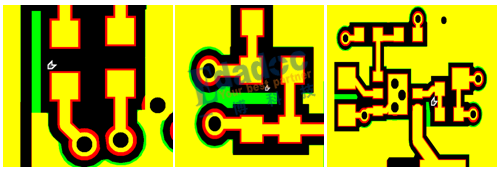

还有一种是两端都不与大铜面连接,孤立的铜皮。如下图:' J6 G. o2 H9 I* d- f. D# h+ L

还有一种是两端都不与大铜面连接,孤立的铜皮。如下图:' J6 G. o2 H9 I* d- f. D# h+ L 危害:

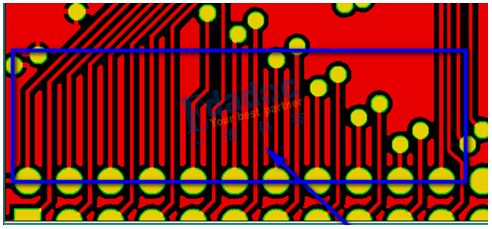

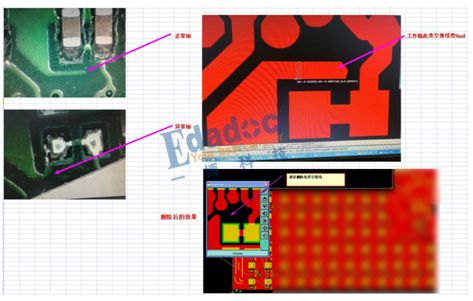

危害: 下面为正常和异常的比对图片。! I1 J3 m+ S: k+ M

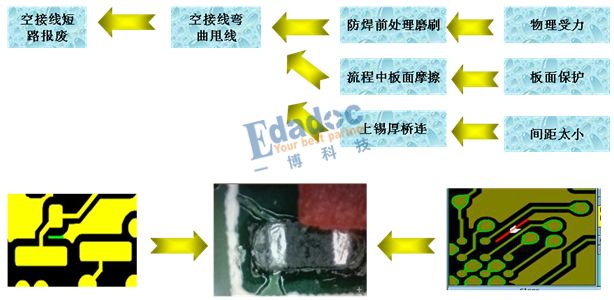

下面为正常和异常的比对图片。! I1 J3 m+ S: k+ M 形成过程如下:" K7 J0 C9 G' F$ A- P/ l* M

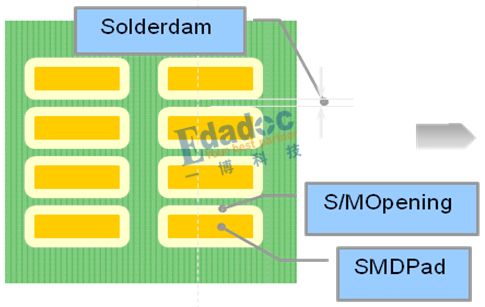

形成过程如下:" K7 J0 C9 G' F$ A- P/ l* M 下面为正常的阻焊开窗示意图:

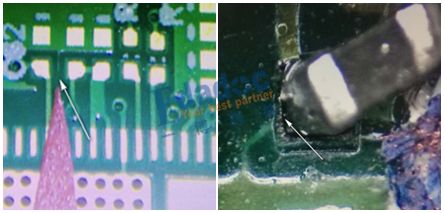

下面为正常的阻焊开窗示意图: 正常的一个阻焊封装建立,为了防止在阻焊工序曝光时对位的偏移,导致在显影时油墨上焊盘,通常阻焊开窗比SMD焊盘单边大2mil,整体大4mil.。

正常的一个阻焊封装建立,为了防止在阻焊工序曝光时对位的偏移,导致在显影时油墨上焊盘,通常阻焊开窗比SMD焊盘单边大2mil,整体大4mil.。 上图为实际板子上单边2mil的净空区。

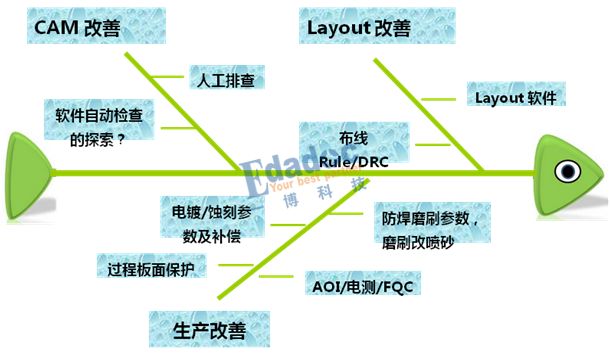

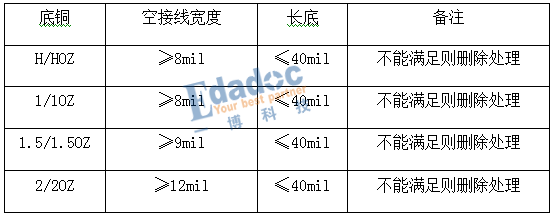

上图为实际板子上单边2mil的净空区。 从上图我们可以看出,除了在生产时认真管控外,造成空接线最基本的原因还是PCB原设计和工厂CAM制作的优化影响很大。对此我们设计工程师在设计时,如果空接线的铜皮宽度小于下面列表中数据,我们最好把其优化掉。

从上图我们可以看出,除了在生产时认真管控外,造成空接线最基本的原因还是PCB原设计和工厂CAM制作的优化影响很大。对此我们设计工程师在设计时,如果空接线的铜皮宽度小于下面列表中数据,我们最好把其优化掉。 现实总是给人一棍闷击,让人没有还手之力。

现实总是给人一棍闷击,让人没有还手之力。 & H1 ], m2 v& w1 }

& H1 ], m2 v& w1 }| 欢迎光临 EDA365电子工程师网 (http://bbs.elecnest.cn/) | Powered by Discuz! X3.2 |