结果,SI工程师没有同意投板,却提出了不合常理的时序要求,如下图所示:

结果,SI工程师没有同意投板,却提出了不合常理的时序要求,如下图所示:

瞬间感觉自己很委屈,这样的等长到时候地址控制线之间的延时会相差100ps左右,这样时序的margin就会变小,甚至可能跑不到要求的2400Mbps,于是硬气的提出了自己的质疑。/ J, y$ ~$ f* |* |: i* w4 b4 R

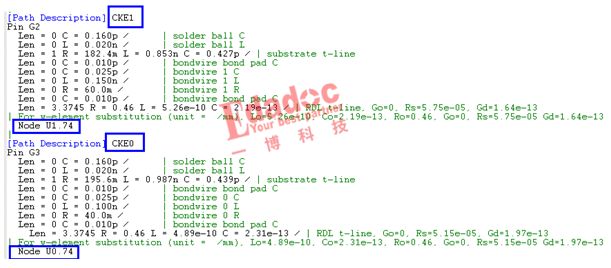

瞬间感觉自己很委屈,这样的等长到时候地址控制线之间的延时会相差100ps左右,这样时序的margin就会变小,甚至可能跑不到要求的2400Mbps,于是硬气的提出了自己的质疑。/ J, y$ ~$ f* |* |: i* w4 b4 R 这种情况的原因不是因为设计人员的误操作,或者不同层的时序不一致,也不是像上次文章中提到的层叠中的DK设置不一样,而是因为DDR颗粒的选型导致的,如下面图片所示:

这种情况的原因不是因为设计人员的误操作,或者不同层的时序不一致,也不是像上次文章中提到的层叠中的DK设置不一样,而是因为DDR颗粒的选型导致的,如下面图片所示:

这款SDRAM的CS,CKE,ODT为单DIE结构,但是其他的信号却是双DIE结构,在封装中做T型拓扑,这样意味着双DIE的信号的容性更大一些,那么相应的上升沿会更缓一些,这个是比较好的影响,这样的话,信号质量会比较好,从图中的结果也可以看出来,绿色信号的振铃比较小。另一个影响是容性更大,意味着时延会更慢一些,所以相同等长的情况下,由于颗粒内部拓扑的影响,导致CMD信号会传输的更慢一些,体现在仿真结果中,自然是双DIE信号和单DIE信号会有不一样的上升沿和一定的延时差。! V! h0 q0 N8 U& |9 U9 {( Z& r5 H5 t

这款SDRAM的CS,CKE,ODT为单DIE结构,但是其他的信号却是双DIE结构,在封装中做T型拓扑,这样意味着双DIE的信号的容性更大一些,那么相应的上升沿会更缓一些,这个是比较好的影响,这样的话,信号质量会比较好,从图中的结果也可以看出来,绿色信号的振铃比较小。另一个影响是容性更大,意味着时延会更慢一些,所以相同等长的情况下,由于颗粒内部拓扑的影响,导致CMD信号会传输的更慢一些,体现在仿真结果中,自然是双DIE信号和单DIE信号会有不一样的上升沿和一定的延时差。! V! h0 q0 N8 U& |9 U9 {( Z& r5 H5 t

+ l/ F. p: J! p e- i4 @8 l* B

+ l/ F. p: J! p e- i4 @8 l* B

揭开一个等长不等时的“骗局”

揭开一个等长不等时的“骗局” 宝藏文,高速先生所有原创技术文章,戳戳戳!2 d1 H Q) f3 u8 X8 @: g( }

宝藏文,高速先生所有原创技术文章,戳戳戳!2 d1 H Q) f3 u8 X8 @: g( }

| 欢迎光临 EDA365电子工程师网 (http://bbs.elecnest.cn/) | Powered by Discuz! X3.2 |